## Aus dem Institut für IT-Sicherheit der Universität zu Lübeck Direktor: Prof. Dr.-Ing. Thomas Eisenbarth

## Software Defenses against CPU Side-Channels

Inauguraldissertation zur Erlangung der Doktorwürde der Universität zu Lübeck

Aus der Sektion Informatik / Technik

vorgelegt von Jan Wichelmann aus Vechta

Lübeck, 2024

- 1. Berichterstatter: Prof. Dr.-Ing. Thomas Eisenbarth

- 2. Berichterstatter: Prof. Dr. Daniel Gruss

Tag der mündlichen Prüfung: 02. August 2024

Zum Druck genehmigt. Lübeck, den 14. August 2024

## Abstract

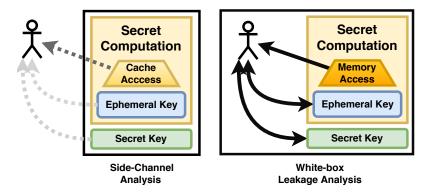

Side-channel attacks on CPUs allow crossing architectural security barriers which were deemed impenetrable by software. Even trusted execution environments (TEEs), which seek strong hardware-based isolation of applications running on an untrusted system, have been subject to attacks which managed to extract the code and data inside them. Attack techniques range from tracking memory access patterns via cache attacks to single-stepping of TEEs, deducing secrets from ciphertext changes in memory, and even invoking transient behavior that yields state which should not be accessible by software at all.

We begin this thesis with an overview over the various side-channel attack techniques and highlight their capabilities. We then take a defender's perspective, aiming to deploy side-channel resistant software. The most common class of side-channel vulnerabilities in software concerns memory access pattern leakages, where the attacker can infer secrets by observing secret-dependent control flow and memory accesses. Absent effective hardware countermeasures against side-channels, the standard solution for such leakages is constant-time code, which exhibits access patterns that are independent from secrets. However, writing such code is complex and error-prone, prompting research into automatic leakage detection. To date, there are many different proposals for finding side-channel leakages in software, with varying focus on soundness, capabilities and scalability. We survey the existing research and propose a new framework Microwalk, which aims to unite the features of the different techniques in a single practically usable tool.

Progressing forward, we discuss side-channel defenses which do not need as much manual intervention by the developer and comprise both hardware and software approaches. We propose Cipherfix, which automatically rewrites binaries to be resistant to ciphertext side-channel attacks, an attack method allowing to break constant-time implementations on TEEs that use deterministic memory encryption schemes. We conclude with Obelix, a dynamic obfuscation engine that addresses many classes of side-channels in a single drop-in solution, including memory access pattern leakages, single-stepping and ciphertext side-channels.

## Kurzfassung

Seitenkanalangriffe auf CPUs überwinden architekturelle Sicherheitsbarrieren, die für Software als undurchdringlich galten. Selbst Trusted Execution Environments (TEEs), die eine starke hardwarebasierte Isolation von Anwendungen auf einem nicht vertrauenswürdigem System anstreben, waren Ziel von Angriffen, denen es gelang, Code and Daten aus diesen Umgebungen zu extrahieren. Angriffstechniken reichen hierbei vom Mitschneiden von Speicherzugriffsmustern mittels Cache-Angriffen bis hin zum Single-Stepping von TEEs, Ableiten von Geheimnissen aus Chiffretextänderungen im Speicher und sogar Verursachen von transientem Verhalten, das zu für Software unerreichbaren Systemzuständen führt.

Wir beginnen diese Arbeit mit einem Überblick über die verschiedenen Seitenkanal-Angriffstechniken und ihre Fähigkeiten. Anschließend nehmen wir die Perspektive eines Verteidigers ein, der seitenkanalresistente Software entwickeln und einsetzen möchte. Die häufigste Klasse von Seitenkanal-Schwachstellen sind Lecks von Speicherzugriffsmustern, aus denen der Angreifer durch Beobachtung von geheimnisabhängigen Kontrollflüssen und Speicherzugriffen auf Geheimnisse schließen kann. Mangels effektiver Hardware-Gegenmaßnahmen gegen solche Schwachstellen besteht die Standardlösung in constant-time Code, dessen Zugriffsmuster unabhängig von geheimen Eingaben sind. Das Schreiben solchen Codes ist jedoch komplex und fehleranfällig, was Forschung zur automatischen Schwachstellenerkennung veranlasst hat. Inzwischen gibt es viele verschiedene Vorschläge zur Erkennung von Seitenkanal-Schwachstellen in Software, mit variierendem Schwerpunkt auf Korrektheit, Fähigkeiten oder Skalierbarkeit. Wir geben einen Überblick über die bestehende Forschung und schlagen ein neues Framework mit dem Namen Microwalk vor, welches zum Ziel hat, die Merkmale der verschiedenen Techniken in einem praktisch nutzbaren Werkzeug zu vereinen.

Im Anschluss diskutieren wir Seitenkanal-Gegenmaßnahmen, die weniger manuelle Eingriffe seitens des Entwicklers benötigen und sowohl software- als auch hardwarebasierte Ansätze umfassen. Wir schlagen Cipherfix vor, das Binärdateien automatisch umschreibt, um diese gegen Chiffretext-Seitenkanalangriffe resistent zu machen. Chiffretext-Seitenkanäle ermöglichen es, constant-time Implementierungen zu brechen, wenn diese auf TEEs mit deterministischer Speicherverschlüsselung laufen. Zum Abschluss stellen wir Obelix vor, das mittels dynamischer Obfuscation viele Klassen von Seitenkanalangriffen in einer einzigen direkt einsetzbaren Lösung behebt, insbesondere Speicherzugriffsmuster-Lecks, Single-Stepping und Chiffretext-Seitenkanäle.

## Acknowledgements

First of all, I would like to thank my advisor Thomas for offering me this opportunity and mentoring my research. The combination of seemingly endless patience, approachability, humor and will to let me set my own priorities contributed to a great work environment.

I would also like to thank my many colleagues, students and collaborators, some of whom I have even learned to call friends. Thank you for the fun time, for enduring my odd puns and machine learning jokes, and of course for many insightful discussions. Specifically, thank you Luca, for our numerous collaborations when designing SEV attacks and for still wanting to work with me even after I repeatedly rewrote half of the paper; Anja Rabich for doing the Obelix measurements an x-th time and re-rendering the plots an y-th time; Florian for the help with repetitive paper evaluations; Jonas for asking the right innocent question at the right random time, reviving our stuck debugging efforts more than once; Ines for her advice and help when organizing teaching and navigating administrative depths; Anja Köhl for reliably helping in the Cybersecurity course over many years; and Anna, Paula, Johannes, Pajam and Tim for some very fun lunch breaks and evenings with interesting discussions over unexpected topics.

I can say with certainty that this work would not have turned out the way it did if it weren't for Anna, who has been a constant throughout my entire PhD time. I sometimes (but only sometimes) miss our months-long debugging sessions after we had the brilliant idea of implementing our own binary rewriting engine ("almost done, just this one last bug"), an endeavor which only marked the beginning of some fantastic teamwork. Thank you Anna for many productive discussions, for our seamless joint paper writing, for proof-reading this thesis, and for your support and optimism whenever things looked not as bright for a moment.

Thank you Noemi for introducing me to some of my favorite series and for being available for so many entertaining activities during our study and subsequent PhD phase, providing a welcome break whenever things got stressful.

I could also always rely on my family throughout highs and lows during my study and PhD, providing advice and help whenever needed, which I am very grateful for.

х

Finally, I have to express my deep gratitude to my better half, Sonja, for still being with me after ten years of "will be there in at most 5 minutes, just quickly finishing this piece of code!", for listening to all those rants about whatever went wrong that day, and for nudging me to finally complete this thesis. Thank you for your unending patience and support.

# Contents

| I | So                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | oftwar   | e Defenses against CPU Side-Channels | 1  |  |  |  |  |  |  |  |  |  |  |  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|

| 1 | Introduction       1.1       Main Contributions       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1       1.1 |          |                                      |    |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.1.1    | Individual Publications              | 6  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                      | 9  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Outlin   | ne                                   | 12 |  |  |  |  |  |  |  |  |  |  |  |

| 2 | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                      |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | System   | n Architecture                       | 13 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.1.1    | Operating System and Address Spaces  | 14 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.1.2    | Virtualization                       | 15 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.1.3    | Caches                               | 16 |  |  |  |  |  |  |  |  |  |  |  |

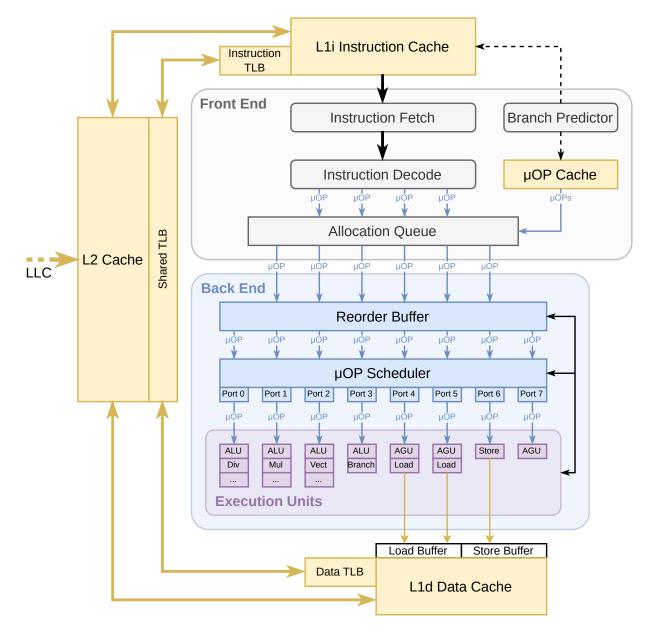

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.1.4    | Execution Engine                     | 18 |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Truste   | d Execution Environments             | 22 |  |  |  |  |  |  |  |  |  |  |  |

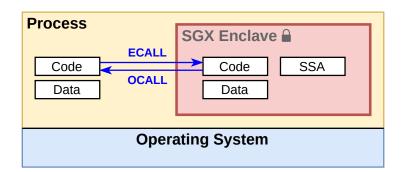

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.2.1    | Process-Level: Intel SGX             | 22 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.2.2    | Virtual Machine Protection: AMD SEV  | 22 |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Softwa   | are Instrumentation                  | 24 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.3.1    | Static Instrumentation               | 24 |  |  |  |  |  |  |  |  |  |  |  |

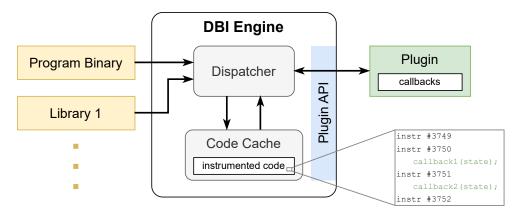

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.3.2    | Dynamic Instrumentation              | 25 |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Code     | Analysis                             | 25 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.4.1    | Symbolic Execution                   | 26 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.4.2    | Taint Analysis                       | 26 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.4.3    | Fuzzing                              | 27 |  |  |  |  |  |  |  |  |  |  |  |

| 3 | Stat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | e of the | e Art                                | 29 |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                      | 29 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.1.1    |                                      | 30 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.1.2    |                                      | 34 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.1.3    |                                      | 35 |  |  |  |  |  |  |  |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.1.4    | Transient Execution                  | 36 |  |  |  |  |  |  |  |  |  |  |  |

|    |       | 3.1.5   | Value-Based Leakages 39    |

|----|-------|---------|----------------------------|

|    |       | 3.1.6   | Other Attacks and Leakages |

|    | 3.2   | Softwa  | re Leakage Analysis        |

|    |       | 3.2.1   | Static Approaches          |

|    |       | 3.2.2   | Dynamic Approaches         |

|    |       | 3.2.3   | Comparison                 |

|    |       | 3.2.4   | Discussion                 |

|    |       | 3.2.5   | Other Vulnerability Types  |

|    | 3.3   | Side-C  | hannel Countermeasures     |

|    |       | 3.3.1   | Cache Attacks              |

|    |       | 3.3.2   | Single-Stepping            |

|    |       | 3.3.3   | Transient Execution        |

|    |       | 3.3.4   | Value-Based Leakages       |

| 4  | Con   | clusior | 1                          |

| Re | feren | ices .  |                            |

| II | Publications |     |  |  |  |  |  |  |  |  |  |  |  |

|----|--------------|-----|--|--|--|--|--|--|--|--|--|--|--|

| 5  | MicroWalk    | 101 |  |  |  |  |  |  |  |  |  |  |  |

| 6  | Microwalk-Cl | 137 |  |  |  |  |  |  |  |  |  |  |  |

| 7  | ΜΑΜΒΟ-Υ      | 177 |  |  |  |  |  |  |  |  |  |  |  |

| 8  | Cipherfix    | 205 |  |  |  |  |  |  |  |  |  |  |  |

| 9  | Obelix       | 247 |  |  |  |  |  |  |  |  |  |  |  |

| III Appendix     |  |  |  |   |       |  |  |      |   |  |   |  |  |  |  |   | 29 | 1 |

|------------------|--|--|--|---|-------|--|--|------|---|--|---|--|--|--|--|---|----|---|

| About the Author |  |  |  | • | <br>• |  |  | <br> | • |  | • |  |  |  |  | • | 29 | 3 |

# Part I

# Software Defenses against CPU Side-Channels

## Introduction

The broad availability of high-bandwidth internet access leads to a centralization of IT services: Instead of maintaining their own data centers, many companies and agencies rent resources on third-party cloud systems. Moving workloads into the cloud avoids the costly acquisition and maintenance of own hardware, and allows quick scaling of applications under an increased load.

However, by moving potentially sensitive computations into the cloud, the customer effectively entrusts the cloud provider with maintaining confidentiality of their applications and isolating them from the applications of other customers. A standard measure to keep customers running on the same hardware from interfering with each other is *virtualization*: Every customer's code runs in a separate *virtual machine* (VM), which is assigned a share of the system's resources and behaves like a native bare-metal system. VMs are managed by the hypervisor (i.e., cloud provider) and cannot access each other's code and data.

If the owner of sensitive code and data does *not* trust the cloud provider, virtualization becomes insufficient, as the hypervisor has full access to all code and data on the given system. Instead, the customer may choose to use a *trusted execution environment* (TEE), which adds an additional layer of hardware-enforced protection that even resists privileged attacks from the hypervisor itself. While VMs can be freely modified by the hypervisor, TEEs encrypt the application's memory and do not allow any other user to read or manipulate it.

Unfortunately, it was shown countless times that the isolation guarantees from VMs and TEEs do not hold in practice. While direct, *architectural* attacks were quickly patched in subsequent processor generations [160, 161, 250, 252], there is another attack class that is much harder to mitigate: *Side-channel attacks*. A side-channel attack does not directly read sensitive information, but *observes* the execution behavior of a program to infer secrets *indirectly*. This reaches from very simple attacks like measuring the total execution time of a program that compares passwords and aborts upon the first difference (thus leaking the amount of correct characters) to complex attacks that exploit a certain behavior of the *hardware* that the program runs on. The latter class, so-called *microarchitectural* side-channel attacks, exploit optimizations that were introduced by

the processor vendors and are transparent to the application developer, like caching [30, 171] or out-of-order execution [144]. TEEs with their powerful attacker model come with another set of attacks, which allow the hypervisor to single-step code [45] or infer secrets from ciphertext changes in memory [136, 138].

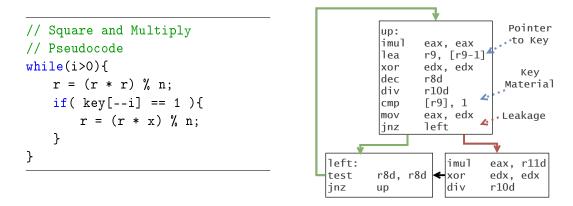

The indirect nature of these attacks makes it difficult to implement effective hardware countermeasures without sacrificing performance, and many such proposals have eventually been shown to be vulnerable to an improved version of the same attack. However, there are mitigations that address at least *some* of the most relevant attack classes and that can be implemented by software developers. The arguably most common type of side-channel leakage are *secret-dependent operations*, also called *memory access pattern leakages*. Common examples are executing an if statement depending on the value of a secret key bit, or using a key byte as index for an array access. Both can be observed by an attacker monitoring memory accesses, e.g., via a cache attack. While the developer of a sensitive application (e.g., cryptographic software) should not be responsible for addressing security issues stemming from unrelated hardware optimizations, they can adapt their software in a way that it becomes resistant against such side-channels.

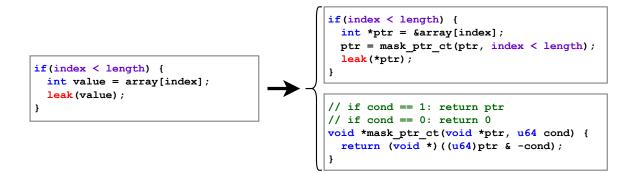

To remove memory access pattern leakages (and thus prevent all attacks exploiting them), the developer systematically replaces secret-dependent operations in their program by *linearized* ones, such that the program always accesses the same code and data, independent from its secret input. Such programs are called *constant-time*, as they exhibit the same observable execution behavior for any input. Writing constant-time code is challenging and prone to missing subtle leakages which may be exploitable nonetheless [16, 208, 239]. As standard bug-finding tools and sanitizers are not capable of finding side-channel leakages, specialized tools and approaches were developed that aim to help the developer identify missed leakages in their code and patch them appropriately. Methods vary from static analysis and proof generation to dynamic analysis and fuzzing [78].

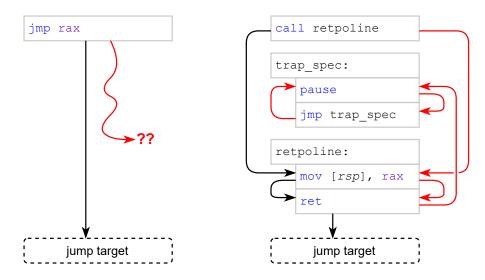

Other research goes one step further and designs tools that *automate* code hardening through means like static instrumentation. For example, it is possible to automatically linearize code, allowing developers to write leaking, but better maintainable code, that is later transformed by the compiler. Such automated hardening tools can also be created for other side-channel attack classes. Several software-only and software/hardware codesign approaches have been proposed for preventing speculative execution attacks [49, 62], TEE single-stepping [55, 59, 168, 246] and ciphertext side-channels [244, 246].

### **1.1 Main Contributions**

In this thesis, we design new side-channel leakage analysis techniques and build automated hardening tools for software running in insecure TEEs.

We advance the state of the art of software defenses against CPU side-channels by:

- Designing a practical dynamic side-channel leakage analysis framework. With Microwalk, we build a new software leakage analysis framework targeted at practical use in day-to-day development. We propose new efficient leakage analysis algorithms based on comparing execution traces generated through dynamic binary instrumentation (DBI). The framework satisfies three key objectives of practical leakage analysis: *Localization* and *quantification* of side-channel leakages, and *efficiency* of the analysis method. We design a modular and extensible framework and devise templates for easy inclusion in Continuous Integration (CI) pipelines. We successfully use Microwalk to uncover many previously unknown side-channel vulnerabilities, which includes leakages in closed-source libraries like Microsoft CNG, that is shipped with every Windows system but received little scrutiny beforehand.

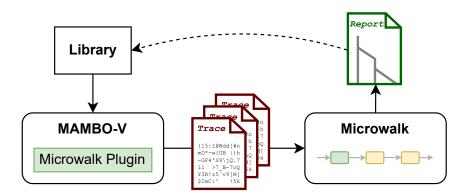

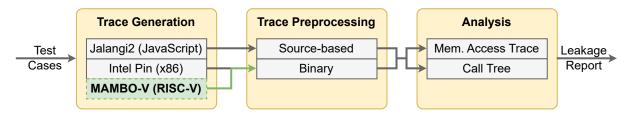

- Bringing dynamic leakage analysis to scripting languages and non-x86 platforms. We show that side-channel leakage analysis algorithms designed for evaluating binaries can also be applied to programming languages directly. For this, we employ source-based static instrumentation to insert trace generation code at relevant source locations. With a custom preprocessor we convert those traces into the generic trace format of Microwalk, allowing us to reuse its existing analysis modules. Using the extended framework, we conduct the first broad leakage analysis of popular JavaScript cryptographic libraries from NPM, identifying many vulnerabilities.

Finally, we demonstrate the first side-channel leakage analysis toolchain for the RISC-V platform. We port the ARM-based DBI framework MAMBO to RISC-V, allowing us to generate native execution traces on RISC-V, which we can subsequently analyze with Microwalk. We hope that the early availability of leakage analysis tooling on RISC-V supports the development of native cryptographic code that is resistant to side-channels from day one.

• Designing an automated software hardening scheme against ciphertext sidechannels. As ciphertext side-channels are specific to TEEs, existing software does not deploy any suitable countermeasures and, due to their impact on code maintainability, is also not likely to deploy them in the future. Starting from a taint tracking tool that collects memory loads and stores that access secret data and are potentially vulnerable against ciphertext side-channel attacks, we build an automatic software hardening framework based on rewriting existing binaries. We complement each memory write with additional instructions which generate a new random mask and add this mask to the written value, leading to fresh ciphertexts. We evaluate different methods for sampling sufficiently good randomness and for keeping track of the secrecy of a given memory location. We apply our toolchain to several popular cryptographic implementations and show that it can protect them against ciphertext side-channel attacks with a reasonable runtime overhead.

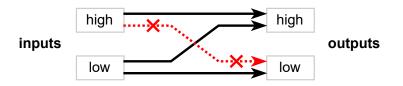

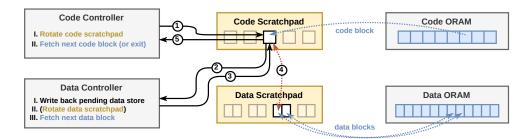

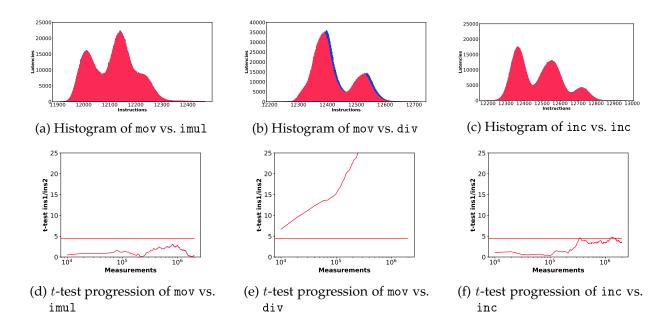

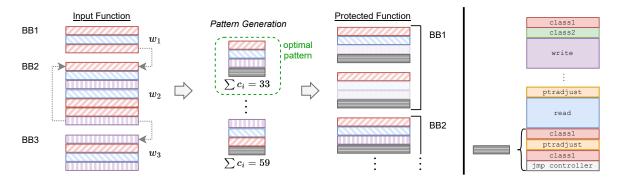

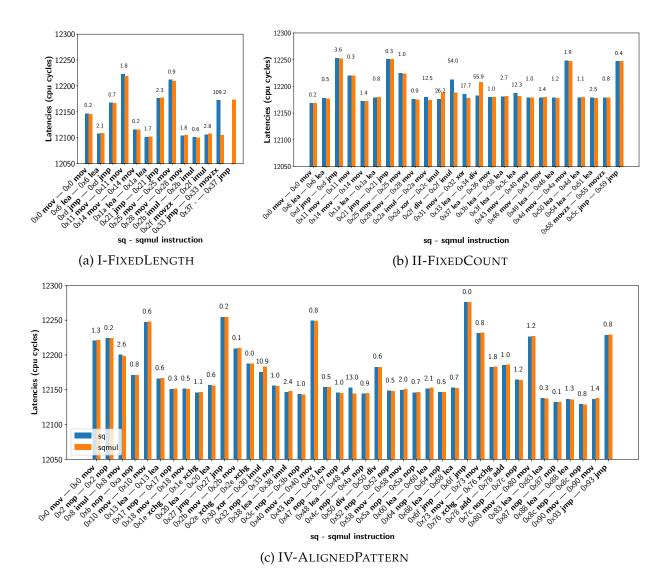

• Exploring a catch-all drop-in software countermeasure against a wide spectrum of TEE-related attacks. We survey existing software countermeasures against the high variety of side-channel attacks against TEEs, and find that these countermeasures only cover few attack vectors and often require expert knowledge to apply. With the objective of "restoring trust in TEEs" we look for an automated solution that can protect against *all* relevant classes of attacks, and explore the suitability of a rather exotic approach: Full program obfuscation. We show how an existing obfuscation tool can be adapted to protect against timing and controlled channel attacks, single-stepping and ciphertext side-channels. For this, we analyze the practical capabilities of single-stepping attackers on Intel SGX and AMD SEV, and design an algorithm that generates corresponding indistinguishable code blocks. In our evaluation we find that, while the resulting tool comes with a high performance overhead, it can reliably protect entire cryptographic implementations against attackers trying to fingerprint code or extract secret data.

#### 1.1.1 Individual Publications

In the following, we summarize the individual publications included in this thesis, which make up the main contributions. The respective full text is given in Part II.

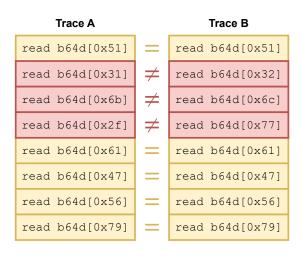

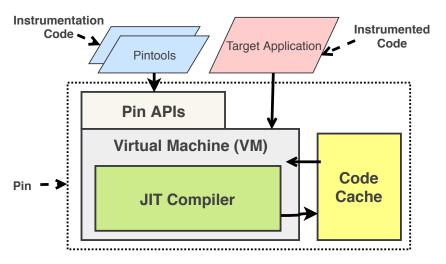

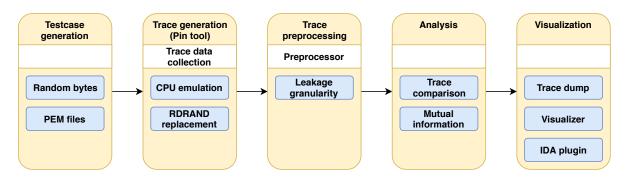

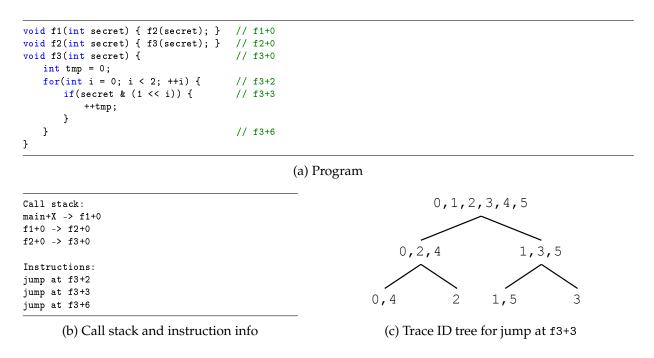

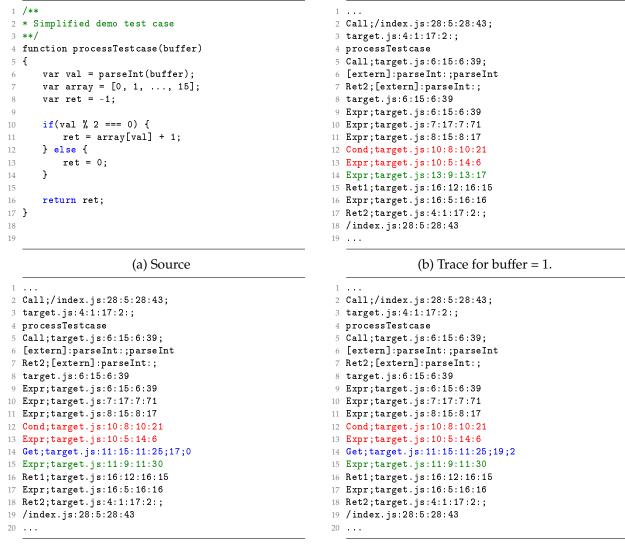

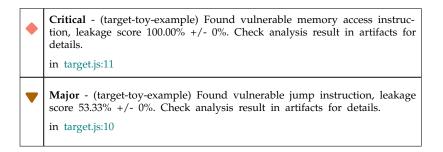

**Microwalk: A Framework for Finding Side Channels in Binaries.** To avert sidechannel vulnerabilities caused by the microarchitecture a program is executed on, programmers need to employ software-based mitigation techniques. One such technique is constant-time code, i.e., code that exhibits the same control flow and memory access patterns independent from a secret input. There are various ways to verify whether a given program is constant-time, but to this point research mostly focused on static analysis (which tends to be slow and hard to deploy in practice) and on imprecise or highly manual methods. We introduced a new fast dynamic leakage analysis method based on DBI and mutual information analysis: First, we generated a number of random secret inputs and collected corresponding execution traces. We then compared those traces with a focus on the observed memory access patterns. Any difference between two traces is directly linked to a secret-dependent computation, which is potentially exploitable by a side-channel attacker. As the approach tends to find many potential vulnerabilities in a program, we assigned them a severity score, which is the mutual information between the secret input and the resulting trace.

We implemented the workflow in a new modular and extensible framework, Microwalk. With Microwalk, we showed that our leakage analysis technique can efficiently find side-channel leakages in cryptographic libraries, and we uncovered previously unknown leakages in the closed-source Microsoft CNG and Intel IPP cryptographic libraries.

The paper was published at *ACSAC 2018* in collaboration with Daniel Moghimi, Thomas Eisenbarth, and Berk Sunar [243]. The full text is in Chapter 5.

**Microwalk-Cl: Practical Side-Channel Analysis for JavaScript Applications.** While side-channel leakage analysis of software is a well-studied problem, the results never found wide practical adoption, mostly since the research artifacts were hardly usable, had bad performance, or required in-depth knowledge of the underlying methods. For these reasons, as was shown by a study in 2022 [118], developers of cryptographic libraries still heavily relied on occasional vulnerability disclosures by researchers and, in some cases, on manual code analysis through tools like ctgrind [133].

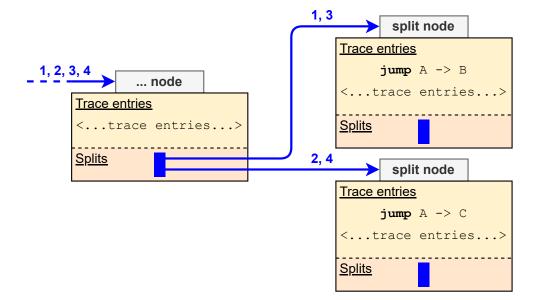

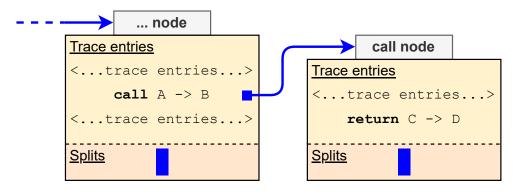

To address these challenges, we developed a new dynamic leakage analysis algorithm, which inserts the execution traces into a trie-like data structure, allowing precise localization and quantification of potential leakages in linear time. As mutual information alone gives misleading results in some cases, we evaluated alternative leakage measurement methods. The result is a single scalar leakage score which is shown to the user, so they can quickly prioritize the reported leakages. In another contribution, we abstracted Microwalk's trace generation stage to support arbitrary programming languages, and showed how one can generate suitable execution traces even for script languages like JavaScript.

Finally, we showed how one can design a general-purpose analysis template for the extended Microwalk framework, which abstracts away most configuration complexity and allows a developer to easily integrate side-channel leakage analysis into their existing Continuous Integration workflow. The Docker images, configuration templates and example repositories were made available at GitHub [154]. We used the new toolchain to do the first thorough leakage analysis of popular cryptographic libraries on NPM, and uncovered many vulnerabilities.

The paper was published at *ACM CCS 2022* in collaboration with Florian Sieck, Anna Pätschke and Thomas Eisenbarth [247]. The full text is in Chapter 6.

**MAMBO-V:** Dynamic Side-Channel Leakage Analysis on RISC-V. Most existing leakage analysis tools target source code or x86 binaries. While analyzing source code can find source-level leakages, it misses vulnerabilities introduced by compiler optimizations. Binary approaches catch such issues, but they are inherently bound to a certain architecture. It is desirable to have leakage analysis support on other platforms as well, especially on the upcoming RISC-V architecture which is growing quickly, to avoid repeating the many security issues from x86 and ARM. As no DBI tool for RISC-V was available, we created a port of the ARM-based DBI tool MAMBO, naming it MAMBO-V. We used MAMBO-V to generate Microwalk-compatible execution traces for RISC-V binaries, allowing us to conduct the first side-channel leakage analysis of native RISC-V cryptographic code. We identified several vulnerabilities, mostly caused by insecure fallback implementations in popular libraries which do not yet offer assembly implementations optimized for RISC-V.

The paper was published at *DIMVA 2023* in collaboration with Christopher Peredy, Florian Sieck, Anna Pätschke and Thomas Eisenbarth [245]. The full text is in Chapter 7.

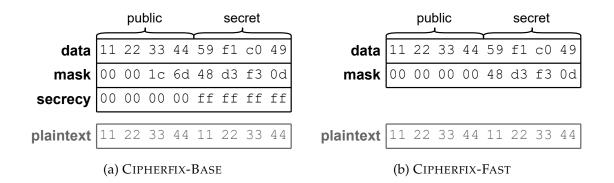

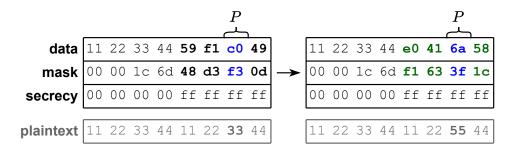

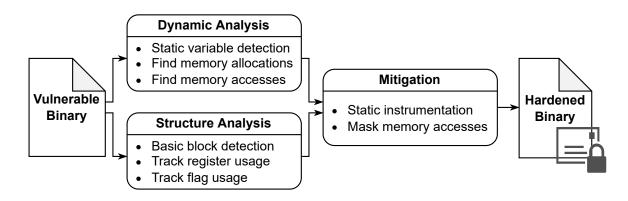

**Cipherfix: Mitigating Ciphertext Side-Channel Attacks in Software.** Ciphertext side-channels are a rather young attack class, targeting deterministic memory encryption in TEEs (in this case, AMD SEV). They exploit the fact that a fixed plaintext always results in the same ciphertexts at a certain memory address, allowing the attacker to detect repeating plaintexts by keeping track of observed ciphertexts. They can then use this information to break constant-time cryptographic implementations. As hardware-based countermeasures are not available, software hardening is necessary. We solved this problem through masking, where we added a random value each time data was written to memory. When reading the data, the mask was subtracted again.

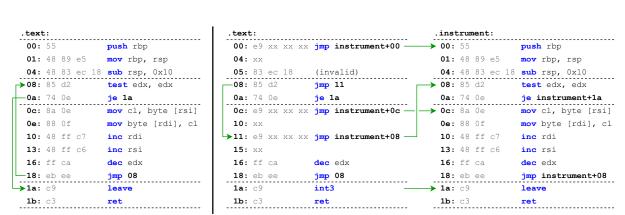

As simply masking all data was not efficient, we prepended an analysis step, where we used dynamic taint tracking to find all locations where secret data was processed, and did precise context-aware tracking of stack variables and heap allocations to find where those secrets were stored. We then implemented a static binary instrumentation tool, which rewrote the relevant memory loads and stores to use masking. Due to our binary approach, we could harden a program across library boundaries without requiring recompilation. We showed that the resulting performance overhead was tolerable, and discussed possible trade-offs between performance and security, like the bookkeeping of secrecy information and the choice of the random number generator for the masks.

The paper was published at *USENIX Security* 2023 in collaboration with Anna Pätschke, Luca Wilke und Thomas Eisenbarth [244]. The full text is in Chapter 8.

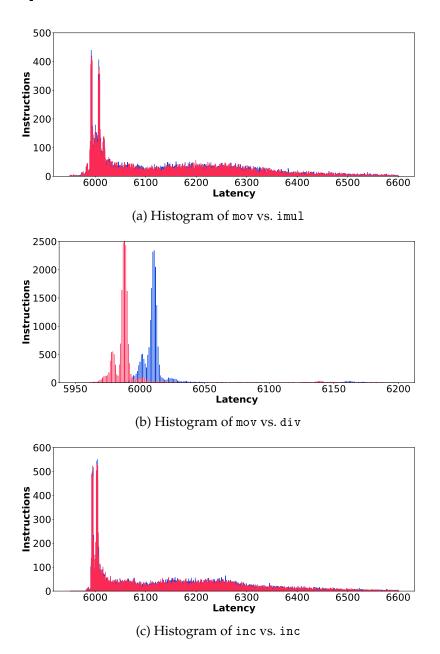

**Obelix: Mitigating Side-Channels through Dynamic Obfuscation.** Over time many different side-channel attacks were demonstrated against TEEs. Some were addressed through hardware updates, but many must be averted by software countermeasures. However, the existing countermeasures only focus on single attack classes, are incompatible with each other, or can only protect the secret data within the TEE, but not hide the code itself. We designed a drop-in mitigation that can prevent a wide range of side-channel attacks and manages to protect both code and data. Our approach was based on dynamic obfuscation, where code and data were stored in oblivious memory and fetched block by block. To protect against single-stepping, we built the blocks in a way that they are indistinguishable for a high-resolution attacker, and verified this through precise measurements on Intel SGX and AMD SEV. While the obfuscation-based approach led to a high performance overhead in our proof-of-concept implementation, it is suitable to thoroughly protect small or asynchronously executed programs against all relevant side-channels. Due to the modular design of <code>0belix</code>, it can be extended to also protect against transient execution and fault injection attacks.

The paper was published at *IEEE S&P 2024* in collaboration with Anja Rabich, Anna Pätschke and Thomas Eisenbarth [246]. The full text is in Chapter 9.

### **1.2 Other Contributions**

Apart from the main contributions outlined previously, the author has also contributed to other results which are not included in this thesis. We briefly summarize them in the following.

**MemJam: A False Dependency Attack against Constant-Time Crypto Implementations.** Most side-channel attacks target structures like the translation look-aside buffer (TLB) or the data and instruction caches. While they were successfully used to break cryptographic implementations, they are limited to a spatial locality of the size of a page or cache line. With MemJam, we demonstrated a new side-channel attack with intra-cache line resolution, that exploits false memory read-after-write dependencies between two hyperthreads. We showed that MemJam can be used to break several cryptographic primitives in the Intel IPP library, which was specifically hardened against cache attacks.

The paper was published in the *Springer IJPP 2019* journal in collaboration with Ahmad Moghimi, Thomas Eisenbarth and Berk Sunar [157].

**SEVurity: No Security Without Integrity – Breaking Integrity-Free Memory Encryption with Minimal Assumptions.** We analyzed the memory encryption of AMD SEV on Zen 1 and Zen 2 platforms. We found that they use an XEX encryption mode with an address-dependent tweak, which we were able to reverse engineer. We then showed how one can construct an initial encryption oracle solely by moving around existing ciphertext blocks in memory. This way, we were able to build a multi-stage exploit which finally allowed us to inject arbitrary code and data into the protected VM, without relying on I/O operations as did previous attacks. As a response to this and other attacks, AMD introduced the SEV-SNP extension, which fixed our attack on Zen 3 by preventing the hypervisor from writing to encrypted memory.

The paper was published at *IEEE S&P* 2020 in collaboration with Luca Wilke, Mathias Morbitzer and Thomas Eisenbarth [250].

#### undeSErVed trust: Exploiting Permutation-Agnostic Remote Attestation.

AMD SEV offers a remote attestation feature which computes a so-called *measurement* of the initial VM state to prove to the VM's owner that the correct bootloader was placed in encrypted memory. To generate the corresponding hash, the hypervisor sequentially calls a dedicated API in the trusted co-processor, passing the code and data which should be stored in encrypted memory. However, we discovered that the measurement did not include the *address* of the data, so we could arbitrarily reorder it in memory, with the measurement not changing as long as we called the API in the right order. This way, the owner of the VM would believe that the bootloader was loaded correctly, and would supply their secret disk encryption key for booting the system. We were able to reorder the code in such a way that we could inject small amounts of data into the VM, which after several steps resulted in a full encryption oracle and control over its execution.

The paper was published at *WOOT 2021* in collaboration with Luca Wilke, Florian Sieck and Thomas Eisenbarth [252].

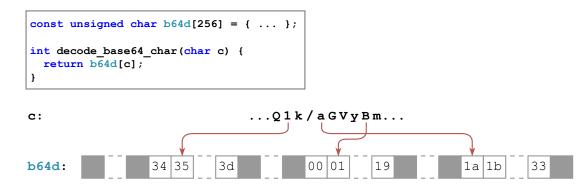

**Util::Lookup: Exploiting key decoding in cryptographic libraries.** We used Microwalk to conduct a leakage analysis of key decoding functions, which were often ignored during side-channel analysis. We found that many libraries implement table-based Base64 decoding, leaking the secret key through the sequence of accessed indexes. However, this is difficult to exploit using conventional cache attacks due to the small amount of leakage (around one bit per Base64 character) and high performance of the implementation. We significantly increased the practically achievable attack precision by combining single-stepping with a cache attack, allowing us to accurately measure each table lookup and then reconstruct the private key. Our attack was aided by a software mitigation recently proposed by Intel to counter Load Value Injection (LVI) attacks, showing that countermeasures against one class of attacks may actually amplify another. The paper was published at *ACM CCS 2021* in collaboration with Florian Sieck, Sebastian Berndt and Thomas Eisenbarth [208].

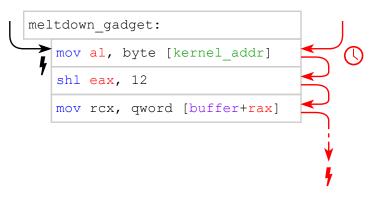

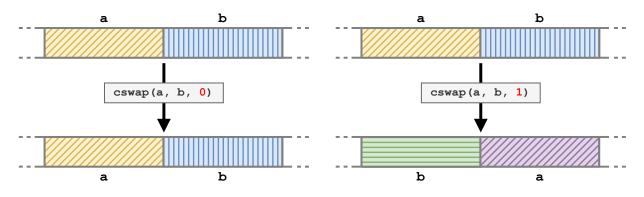

**A Systematic Look at Ciphertext Side Channels on AMD SEV-SNP.** While AMD SEV-SNP includes measures to prevent the hypervisor from moving ciphertexts (which we exploited in our SEVurity and undeSErVed trust papers), it still relies on a deterministic memory encryption. In this work, we systematically analyzed the attack surface exposed by deterministic ciphertexts, and identified two main attack primitives: The dictionary attack, where a certain variable only has few possible values, leading to few distinguishable ciphertexts; and the collision attack, where the attacker only observes whether a variable *changed*, allowing them to break common constant-time primitives like conditional swaps. We showed that ciphertext side-channel attacks can break constant-time cryptographic implementations, and proposed and discussed several potential mitigation approaches.

The paper was published at *IEEE S&P* 2022 in collaboration with Mengyuan Li, Luca Wilke, Thomas Eisenbarth, Radu Teodorescu and Yinqian Zhang [136].

**ASAP: Algorithm Substitution Attacks on Cryptographic Protocols.** In an algorithm substitution attack (ASA), an adversary modifies the shipped implementation of a cryptographic primitive to embed secrets in publicly sent data, which allows them, for example, to leak secret keys. We analyzed the applicability of ASAs on the protocol level, and found that commonly desired properties like forward secrecy and post-compromise security directly enable ASAs. We showed that we can easily hide private keys in nonces used by the TLS and WireGuard protocols, while the Signal protocol is much more robust due to its double ratchet structure.

The paper was published at *ACM AsiaCCS 2022* in collaboration with Sebastian Berndt, Claudius Pott, Tim-Henrik Traving and Thomas Eisenbarth [29].

**Help, my Signal has bad Device!** We analyzed the post-compromise security of Signal when the user's identity key is leaked by an attacker. While existing conversations remain secure under the core Signal protocol, this does not hold for the extensions which allow using Signal on multiple devices. Indeed, we showed that an attacker who possesses the identity key can stealthily register secondary devices under the user's account, allowing them to receive and send all future messages involving the compromised user. We proposed short-term and long-term countermeasures, concluding that the device registration workflow of Signal must be replaced by a more robust protocol to fully avert our attack.

The paper was published at *DIMVA 2021* in collaboration with Sebastian Berndt, Claudius Pott and Thomas Eisenbarth [242].

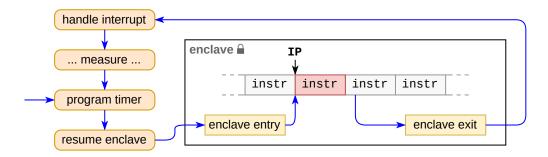

**SEV-Step: A Single-Stepping Framework for AMD-SEV.** Single-stepping is a powerful attack primitive against TEEs. As the name suggests, it allows the malicious hypervisor to step the protected code with instruction granularity, by programming a timer that interrupts the enclave after precisely one instruction. *SGX-Step* [45] offers a software framework that aids in building such attacks on Intel SGX. We showed that single-stepping is also possible on AMD SEV, and designed a framework called *SEV-Step* that offers the necessary infrastructure for single-stepping alongside further attack tools like page-fault tracking and cache attacks. We demonstrated SEV-Step by conducting an end-to-end cache attack against the cryptographic code contained in the Linux operating system, allowing us to obtain the volume key of a LUKS2-encrypted disk. In addition, we conducted precise measurements indicating that *Nemesis*-style [44] instruction latency measurement attacks also apply to AMD SEV.

The paper will appear at *CHES* 2024 and was written in collaboration with Luca Wilke, Anja Rabich and Thomas Eisenbarth [251].

## 1.3 Outline

This thesis is structured in two parts. In the first part, after providing fundamental background on system architecture and microarchitecture, code analysis and software instrumentation in Chapter 2, we discuss the state of the art in side-channel attacks and defenses in Chapter 3. More precisely, we first summarize the many different classes of side-channel attacks and typical software-level leakages (Section 3.1). Then, we survey automated software leakage detection techniques and discuss the advantages and drawbacks of each approach (Section 3.2). Finally, we give an overview over manual and automated side-channel defenses, comparing both hardware- and software-oriented proposals (Section 3.3). In Chapter 4 we conclude the first part of this thesis and give an outlook on open questions and future research.

The second part then follows with the publications making up the main contributions of this thesis, in their original peer-reviewed text.

2

## Background

In this chapter, we give some background necessary for following the contributions of this thesis. For the side-channel attacks and defenses, we provide an overview over common system architecture and trusted execution environments. In addition, as we later discuss software leakage analysis and automated code hardening in-depth, we need a general understanding of software instrumentation and code analysis.

## 2.1 System Architecture

System architecture can be viewed on different levels. At the highest level, most modern computers follow the von Neumann architecture model: A central processing unit (CPU) is connected with main memory and some input/output devices via a number of buses. Software usually relies on this *architectural* view of the system. This thesis mostly focuses on the next two lower levels, which are often referred to as *microarchitecture*: The organization of a CPU into separate physical cores with some shared resources like the last-level cache and memory bus, and the execution engine of a physical core itself. Software typically is oblivious to these layers, though it may contain optimizations to maximize utilization of microarchitectural components.

We start with the architectural view, which involves processes, the operating system, address spaces and virtualization. Afterward, we discuss caches and, finally, a physical core's microarchitecture and the out-of-order and speculative execution optimizations, which are subject to many side-channel attacks.

The following only gives a rough overview over the concepts needed for understanding side-channel attacks, and focuses on the x86-64 architecture. For a more detailed introduction into system architecture, we refer the reader to books like *Computer Architecture* – *A Quantitative Approach* [98] and *Operating Systems: Three Easy Pieces* [18], which also form the foundation of this section.

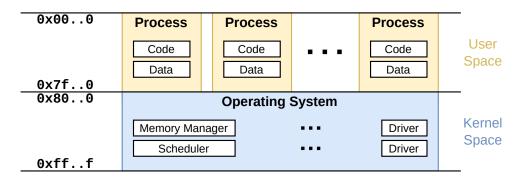

Figure 2.1: Memory layout of modern operating systems. Each process has its own virtual address space, comprising the entire encodable address range. The lower half of the address space (*user space*) belongs to the process itself, and may contain code, data, the heap, the stack and libraries the application depends on. The higher half (*kernel space*) is used by the operating system and is inaccessible by user code. Due to the isolated virtual address spaces, processes can only access their own code and data.

#### 2.1.1 Operating System and Address Spaces

Contrary to embedded devices, general-purpose computers often run many processes in parallel. This requires careful isolation to keep a defective or compromised process from blocking resources, destabilizing the system, or interacting with data from other processes. As a solution, CPUs generally enforce a privilege model, where the (trusted) operating system (OS) runs with the highest privilege and manages many processes running at the lowest privilege level. Depending on the architecture, device drivers may occupy intermediate privilege levels or run with the same privileges as the operating system kernel. The processes themselves are isolated via *virtual address spaces* (Figure 2.1). This means that they can't access physical memory directly, but all accesses are to virtual (linear) addresses which are translated into physical addresses by the processor's memory management unit (MMU). Besides the security benefits, this separation also greatly simplifies software development, as the physical properties of the system are abstracted away and a process only sees its own contiguous, linear address space.

To enable efficient address translation, the virtual-to-physical address mappings are stored as a tree structure, where each node is a table that encodes several bits of the virtual address (9 bits per level on x86). The smallest translation unit is referred to as *page*, which typically has a size of 4096 bytes (4 kB). Consequently, the leafs of the translation tree are called *page tables*. As is common in the side-channel field, we use the term synonymous to the entire tree structure in this thesis, and do not distinguish between the different tree levels.

Page tables are managed by the kernel, which can also define for each page table entry whether the page or sub tree is privileged (*user/supervisor access* bit), whether it is currently

present in physical memory or was swapped out by the OS (*present* bit), or whether the page is writable (*read/write* bit). Other notable page table bits are the *accessed* bit, which is set by the CPU when the page is accessed by a program, and the *no-execute* bit, which prevents the page's data from being interpreted as executable instructions. Common operating systems partition the virtual space into two halves, where the lower half (0x00..0-0x7f..f) belongs to the process and the higher half (0x80..0-0xff..f) maps the kernel. By putting the kernel into the higher half of every process's virtual address space (protected by the *user/supervisor access* bit), system calls become very efficient, as the current address space does not need to be changed during user/kernel mode context switches.

When the process tries to access a virtual address that is not mapped in the current process (or the *present* bit of the corresponding page table entry is not set), a *page fault* exception is raised. This redirects execution to an interrupt handler in the OS, which receives the requested virtual address and may then decide whether the page is made available and the process is resumed afterward, or whether the process is terminated due to an illegal access.

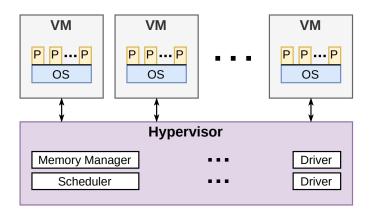

### 2.1.2 Virtualization

In some cases, isolated processes may not suffice, as the user wants to virtualize an entire operating system. A common application for virtualization are cloud services, which host several customers on the same hardware to improve utilization and thus save costs. From the customer's view, their *virtual machine* (VM) looks and behaves like it runs on physical hardware.

As software-emulation through tools like QEMU [28, 182] is inefficient, modern CPUs provide hardware support for virtualization through extensions like Intel VT-x [105, Vol. 3, Ch. 24] or AMD SVM [10, Vol. 2, Ch. 15]. These introduce a new virtualized execution mode. The host operating system becomes the *hypervisor* (Figure 2.2). While the hypervisor may forward certain functionality to the VM, most accesses to system functionality must go through the hypervisor. This commonly happens through interrupts which transfer execution from the VM to the hypervisor.

A notable feature is memory virtualization through *nested paging*, which is hardware support for two layers of page tables: The mapping of host physical addresses (HPAs) to guest physical addresses (GPAs), which is managed by the hypervisor, and the mapping of GPAs to guest virtual addresses, which is done by the operating system inside the VM. When a process running inside the VM tries to access memory, the hardware first conducts a page walk in the VM's page table, and after resolving the GPA does a page walk in the host's page table to find the actual physical address. If a GPA is not mapped,

Figure 2.2: Hardware-assisted virtualization. The host operating system becomes the *hypervisor*, which mostly handles the same tasks as a normal OS, but instead of processes manages one or more virtual machines (VMs). Each VM contains a full operating system itself, which in turn runs its own processes. The hypervisor controls the VMs, handles interrupts and forwards input/output.

the processor raises a nested page fault exception (NPF), which exits the VM and must be handled by the hypervisor. After the page was resolved, the VM is resumed.

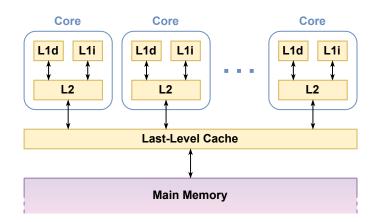

#### 2.1.3 Caches

With growing throughput and parallelism of CPUs, main memory has become a major bottleneck. Both due to the lower frequency and physical distance of main memory, the CPU can process data much faster than it can be retrieved and written back. To address this, CPUs store the current working set in locations that are smaller and more close to the execution units, so-called *caches*. The key observation behind caches is that data is often accessed in a spatially and temporally local manner, i.e., it is likely that an access targets a similar address as a recent access. On common processors, all data (and code) that is used by a CPU core must pass through the cache. If the data is already present there, it can be directly processed. This is called *cache hit*. On the other hand, if the data is not in the cache and must be retrieved from main memory, this is referred to as *cache miss* and comes with a performance penalty.

**Eviction Policies.** As the cache is much smaller than main memory (ranging from kilobytes to few megabytes), the processor must carefully manage its use. The most important component is the *eviction policy*, which controls which address is evicted from the cache to make room for another address. Common policies are (pseudo) *least recently used* (LRU) and random replacement. As the names indicate, (P)LRU removes the address that has been used the longest time ago, while random replacement simply picks a random one. Evicted data is written back into main memory.

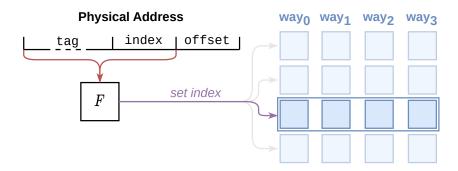

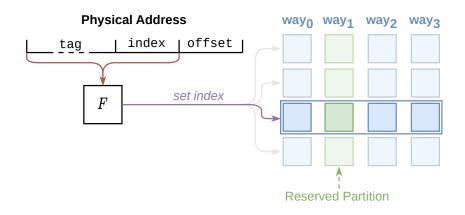

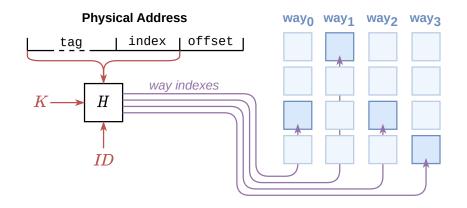

Figure 2.3: A set-associative cache with 4 ways. The tag and index parts of a cache line's physical address are converted into a set index through an arbitrary function F. The set index points to the cache set of that address, which consists of the cells where the cache line can be stored in (one for each way).

**Cache Layout.** To improve efficiency, the entire memory is partitioned into so-called *cache lines*, which usually amount to 64 bytes of data that are treated as a single unit. The physical address of a cached cache line is referred to as its *tag*. There are different methods for assigning cache lines to cache cells.