# Sprint: Secure and Fast Outsourced Machine Learning

Sprint: Sicheres und Schnelles Auslagern von Maschinellem Lernen

### Masterarbeit

im Rahmen des Studiengangs Informatik der Universität zu Lübeck

vorgelegt von Jonas Sebastian Sander

ausgegeben und betreut von **Prof. Dr.-Ing Thomas Eisenbarth**

mit Unterstützung von Ida Bruns, Dr. rer. nat. Sebastian Berndt und Prof. Dr. Esfandiar Mohammadi

Lübeck, den 22. September 2021

# Abstract

Machine learning solutions are moving faster and faster into more and more parts of our society. Cloud providers such as Amazon Web Services, Microsoft Azure, and the Google Cloud Platform, driven by huge profit potentials, aggressively expand their Machine-Learning-as-a-Service offerings. There is a risk that data security and privacy increasingly fall behind.

We investigate the current state of secure outsourcing of ML workloads to the cloud, concentrating on deep convolutional neural networks. We find that the most common and performant mixed SMPC approaches based on homomorphic encryption, secret sharing, and garbled circuits underly a communication overhead that grows linearly in the depth of the neural network. We present Sprint, a scheme for fast and secure outsourcing of ML workloads to the cloud. Sprint is based purely on arithmetic garbled circuits, needs only a single communication round per inference step regardless of the depth of the neural network, and requires compared to recent schemes, a 22 times smaller communication volume for ResNet32.

## Kurzfassung

Lösungen des Maschinellen Lernens erhalten immer schneller in immer weitere Teile unserer Gesellschaft Einzug. Cloud Provider wie Amazon Web Services, Microsoft Azure und die Google Cloud Platform bauen, getrieben durch immense Gewinnpotentiale, aggressiv ihre Machine-Learning-as-a-Service Angebote aus. Es besteht die Gefahr, dass Datensicherheit und Privatsphäre zunehmend ins Hintertreffen geraten.

Wir untersuchen den aktuellen Stand des sicheren Auslagerns von ML Workloads in die Cloud und konzentrieren uns insbesondere auf tiefe Neuronale Faltungsnetze. Dabei stellen wir fest, dass die verbreitetsten und performantesten gemischten SMPC Ansätze basierend auf Techniken der Homomorphen Verschlüsselung, Secret Sharing und Garbled Circuits einem in der Tiefe des Neuronalen Netzes linear wachsenden Kommunikations-Overhead unterliegen. Wir präsentieren Sprint, ein Framework zum schnellen und sicheren auslagern von ML Workloads in die Cloud. Sprint basiert auf einem reinen Arithmetischen Garbled Circuit Ansatz, benötigt unabhängig von der Tiefe des Neuronalen Netzes nur eine einzige Kommunikationsrunde pro Inferenz-Schritt und besitzt im Vergleich zu aktuellen Schemes ein 22-mal kleineres Kommunikationsvolumen für ResNet32.

# Erklärung

Ich versichere an Eides statt, die vorliegende Arbeit selbstständig und nur unter Benutzung der angegebenen Hilfsmittel angefertigt zu haben.

Lübeck, 22. September 2021

## Acknowledgements

An dieser Stelle möchte ich mich zur aller erst bei meinen Eltern und meinen beiden kleinen Geschwistern bedanken. Danke, dass Ihr immer für mich da seid und mir in den paar Frust-Phasen des Studiums mit Rat und Ablenkung zur Seite standet. Das vielleicht wichtigste meines Studiums sind meine Kommilitonen. Ihr seid die Besten und ich möchte mich bei Euch für die unvergessliche Zeit und die vielen schönen und lustigen Erinnerungen bedanken.

Auch die Mitarbeiter des ITS haben mir immer das Gefühl gegeben, willkommen zu sein. Egal, wen ich um Rat gefragt habe, ich bin immer auf Hilfsbereitschaft gestoßen. Besonders möchte ich mich bei Prof. Eisenbarth und Prof. Mohammadi für die Möglichkeit bedanken, eine Masterarbeit mit meinen Lieblingsthemen des Studiums schreiben zu können. Danke Ida für deine Geduld bei der Betreuung meiner Arbeit und den vielen Tipps und Hinweisen zu meinen Texten. Auch möchte ich mich bei Sebastian für die Hilfe bei den Crypto Themen und dem Knobeln an den Half Gates bedanken. Danke Florian für die Hilfestellung bei meinen ersten praktischen Gehversuchen mit Intel SGX. Thanks, Okan, for the discussions about the half gates!

# Contents

| 1 | Intro | oduction                                                          | 1  |  |  |  |  |

|---|-------|-------------------------------------------------------------------|----|--|--|--|--|

|   | 1.1   | Motivation                                                        | 1  |  |  |  |  |

|   | 1.2   | Research Path                                                     | 1  |  |  |  |  |

|   | 1.3   | Organization                                                      | 3  |  |  |  |  |

| 2 | Bac   | kground                                                           | 5  |  |  |  |  |

|   | 2.1   | Machine Learning                                                  | 5  |  |  |  |  |

|   |       | 2.1.1 Linear Regression                                           | 5  |  |  |  |  |

|   |       | 2.1.2 Logistic Regression                                         | 5  |  |  |  |  |

|   |       | 2.1.3 Artificial Neuronal Networks                                | 6  |  |  |  |  |

|   | 2.2   | Secure Multiple-Party Computation and Outsourced Machine Learning | 8  |  |  |  |  |

|   |       | 2.2.1 Ideal/Real Simulation Paradigm                              | 9  |  |  |  |  |

|   |       | 2.2.2 Attacker Models                                             | 10 |  |  |  |  |

|   | 2.3   | Garbled Circuits                                                  | 11 |  |  |  |  |

|   |       | 2.3.1 Oblivious Transfer                                          | 11 |  |  |  |  |

|   |       | 2.3.2 Garbled Circuit Protocol                                    | 11 |  |  |  |  |

|   | 2.4   | Garbled Circuit Optimizations                                     | 13 |  |  |  |  |

|   |       | 2.4.1 Point-and-Permute                                           | 14 |  |  |  |  |

|   |       | 2.4.2 Garbled Row-Reduction 3                                     | 14 |  |  |  |  |

|   |       | 2.4.3 Free-XOR                                                    | 14 |  |  |  |  |

|   |       | 2.4.4 Half Gates                                                  | 15 |  |  |  |  |

|   | 2.5   | Trusted Execution Environments                                    | 16 |  |  |  |  |

|   | 2.6   | Graphical Processing Units                                        | 18 |  |  |  |  |

|   |       | 2.6.1 Memory Spaces                                               | 18 |  |  |  |  |

|   |       | 2.6.2 General-Purpose Computing                                   | 20 |  |  |  |  |

| 3 | Rela  | ated Work                                                         | 23 |  |  |  |  |

|   | 3.1   | Slalom                                                            | 23 |  |  |  |  |

|   | 3.2   | SecureML                                                          | 24 |  |  |  |  |

|   | 3.3   | Oblivious Neuronal Networks via MiniONN Transformations           | 25 |  |  |  |  |

|   | 3.4   | Faster CryptoNets                                                 |    |  |  |  |  |

|   | 3.5   | Delphi                                                            | 27 |  |  |  |  |

|   |       |                                                                   |    |  |  |  |  |

### Contents

| 4                 | Gar  | bling Techniques for Sprint                                    | 29 |

|-------------------|------|----------------------------------------------------------------|----|

|                   | 4.1  | Garbling Gadgets for Arithmetic Circuits                       | 29 |

|                   | 4.2  | Garbled Neuronal Networks                                      | 30 |

|                   |      | 4.2.1 Half-Gate Generalization                                 | 31 |

|                   |      | 4.2.2 Mixed-Modulus Half-Gate                                  | 32 |

|                   |      | 4.2.3 Mixed-Radix Addition                                     | 32 |

|                   |      | 4.2.4 Approximated Garbled Sign                                | 33 |

|                   |      | 4.2.5 Fancy-Garbling                                           | 35 |

|                   | 4.3  | Efficient Garbling with Random Permutations via Fixed-Key AES  | 36 |

| 5                 | Spr  | int: Secure and Fast Outsourced Machine Learning               | 37 |

| 5<br>6<br>7<br>Re | 5.1  | Residue Level                                                  | 37 |

|                   | 5.2  | CRT Level                                                      | 40 |

|                   | 5.3  | ANN Level                                                      | 40 |

|                   | 5.4  | Security                                                       | 41 |

|                   | 5.5  | Implementation                                                 | 41 |

|                   | 5.6  | GPGPU Specifics                                                | 42 |

| 6                 | Per  | formance and Accuracy Evaluation                               | 43 |

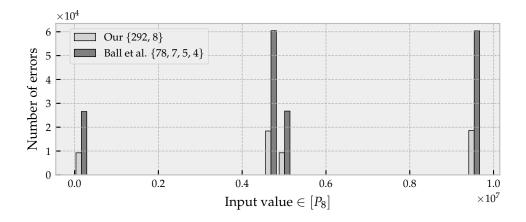

|                   | 6.1  | CRT Representation and the Quantization Constant               | 43 |

|                   | 6.2  | Searching Mixed-Radix Bases and the Approximated Sign Function | 44 |

|                   | 6.3  | Computational Workload in Comparison                           | 45 |

|                   | 6.4  | Online-Communication in Comparison                             | 47 |

|                   | 6.5  | Feature Set in Comparison                                      | 48 |

| 7                 | Con  | nclusion & Outlook                                             | 51 |

|                   | 7.1  | Summary                                                        | 51 |

|                   | 7.2  | Outlook                                                        | 52 |

|                   | 7.3  | Future Work                                                    | 53 |

| Re                | fere | nces                                                           | 55 |

| Ap                | pen  | dix                                                            | 65 |

# Nomenclature

### Abbreviations

| OML | Outsourced Machine Learning   | $\oplus$                | Logical XOR                          |

|-----|-------------------------------|-------------------------|--------------------------------------|

| GC  | Garbled Circuit               | J                       | Error                                |

| HG  | Half Gate                     | L                       | Loss                                 |

| HE  | Homomorphic Encryption        | $x^{(i)}$               | <i>i</i> -th sample of a dataset     |

| SS  | Secret Sharing                | $X^{\{i\}}$             | <i>i</i> -th batch of a dataset      |

| ANN | Artificial Neuronal Network   | $a^{[i]}$               |                                      |

| TEE | Trusted Execution Environment | $a^{\iota \circ \iota}$ | ANN-Activations of layer <i>i</i>    |

| FPU | Fast Processing Unit          | sgn                     | Sign function                        |

| MRS | Mixed-Radix System            | ReLU                    | Rectified Linear Unit function       |

| СРМ | Composite Primorial Modulus   | $sk_a^b$                | Secret key for value $b$ on wire $a$ |

| CRT | Chinese Remainder Theorem     | $\mathrm{EN}_{sk}($     | C) Encrypt C using $sk$              |

Letters and Symbols

xiii

## **1** Introduction

#### 1.1 Motivation

The recent progress of machine learning (ML) with its many technical and practical innovations crosses almost all industries and government institutions while getting more and more applied to security and privacy sensitive domains like healthcare, law enforcement, finance, public administration, logistics, and many more. A large part of these applications require substantial computational resources and while cloud providers push their Machine-Learning-as-a-Service (MLaaS) offerings, the complexity of the hardware and software stacks is continually growing and exposes an expanding surface for potential attackers. A rapidly growing need for methods and techniques for secure and privacypreserving outsourcing of ML applications arises, which moreover meets a political and legal necessity through the General Data Protection Regulation (GDPR) of the European Union and related laws worldwide. In this thesis, we introduce the cryptographic methods used, summarize the current developments in outsourced ML (OML) and research optimization approaches for OML, to further reduce the computational performance gap to conventional ML schemes.

#### 1.2 Research Path

In recent years, artificial neuronal networks (ANNs) have proven to be highly flexible in their application and dominate large areas of the ML landscape. As this class of learning algorithms is highly computational intense, it is especially urgent to develop suitable OML methods. This thesis focuses on the secure outsourcing of ANNs.

We find that Tramèr and Boneh's scheme Slalom [TB19] (see also 3.1), which leverages a trusted execution environment (TEE) and outsources linear workloads to a fast processing unit (FPU) - a hardware accelerator faster than the CPU, is the most promising approach for secure and efficient outsourcing of ANNs. As Slalom's main weakness, we identified the significant communication overhead in the online phase, where after each layer of the outsourced ANN, the TEE and FPU communicate. The communication is necessary because the typical activation functions of ANNs are not homomorphic. The past has shown that in practice, particularly deep neural networks often deliver the best results and therefore incur a high communication overhead in Slalom. This thesis raises the re-

#### 1 Introduction

search question of how the communication between the layers can be reduced or avoided entirely.

Our research path starts in the area of mixed-SMPC OML-approaches for ANNs, which combine secret-sharing (SS), homomorphic encryption (HE), and garbled circuit (GC) based techniques. While HE and SS are efficient regarding linear operations, the non-linear activation functions of ANNs lead to large overheads. Therefore, a typical approach computes the linear components via HE or SS and the activation functions via GCs [CL01, BOP06, OPB07, BFL<sup>+</sup>11, MZ17, LJLA17, RWT<sup>+</sup>18, MR18, MLS<sup>+</sup>20]. Unfortunately, all these approaches have a linear number of communication rounds in the depth of the ANN, and we were not able to switch between SMPC techniques without communicating between ANN-layers<sup>1</sup>.

Following a line of work about OML purely based on GCs [SS08, RRK18, RSC<sup>+</sup>19], we switched the perspective and considered the Slalom setting of a TEE with a co-located FPU from this view. In particular, we follow the work of Marshall Ball et al. on highly optimized arithmetic GCs [BMR16] and ANN-specific GC optimizations [BCM<sup>+</sup>19]. In this way, the Slalom becomes a Sprint. The idea is to garble the whole ANN within the TEE and to accelerate the evaluation of the GC, respectively the ANN-inference, on the FPU. Thus, no communication between the layers of the ANN is needed. During the offline phase, the GC is transferred to the FPU. During the online, phase only the garbled input is sent to the FPU, and the garbled inference result from the FPU to the TEE.

We started by implementing our scheme in abstraction layers on the CPU, planning to port it to the GPU afterward. Unfortunately, with the CPU implementation finished, the time of the thesis was well advanced<sup>2</sup>. The bases for the mixed-radix system (MRS) determined to be performant by Ball et al. [BCM<sup>+</sup>19] were not usable, so we had to implement our own search. Becoming familiar with Nvidia GPUs' and Intel SGXs' hardware characteristics, CUDA programming, the GPU and SGX drivers, and CUDA tools on Linux took considerably more time than planned. In order to develop an efficient and highly parallel graphical processing units (GPU) port of garbled ANNs, a new circuit representation is needed that exposes the parallelism of the gates within the gadgets and ANN layers and takes the memory, cache, and computation properties of the GPU into account. Therefore, we were unfortunately not able to complete the whole GPU port until the submission of the thesis. At the end of this thesis, it is not yet possible to make a concrete evaluation is com-

<sup>&</sup>lt;sup>1</sup>In particular, we have explored the possibilities of SS-based OML approaches such as the GMW protocol and Beaver triples (see chapter 7.3).

<sup>&</sup>lt;sup>2</sup>Implementing arithmetic GC schemes is an error-prone task since all intermediate values of their computations are properly encrypted, randomly permuted, and frequently switch between representations, which massively increase debugging times.

petitive and that Sprint clearly outperforms recent schemes in terms of the communication overhead in the online phase.

#### 1.3 Organization

We start by introducing the necessary background knowledge. First, we introduce the basic concept of ANNs via linear and logistic regression in section 2.1. Then we give a short introduction to the field of secure multi-party computation, including its relation to OML in section 2.2 and explain in a functional way how the GC protocol works in section 2.3. Next, we introduce the practically most relevant optimizations for conventional binary GCs in section 2.4, including point-and-permute, garbled row-reduction 3, free-xor, and half gates. Finally, we briefly introduce the principles of TEEs, particularly Intel SGX in section 2.5 and CUDA-enabled GPUs including the concept of general-purpose computing on graphics processing units (GPGPU) in section 2.6. After introducing the background knowledge, we summarize a selection of important works on OML and evaluate them, especially concerning their performance in the online phase in chapter 3.

Based on the binary GCs and their optimizations, we introduce the garbling techniques for Sprint in chapter 4. We start by introducing the garbling gadgets for mixed-modulus arithmetic GCs in section 4.1, including free addition, free multiplication by a public constant, and a unary projection gate for arbitrary functions. Further, we describe in detail cryptographic and ANN specific optimizations for arithmetic GCs in section 4.2. In particular, these optimizations are used for accelerated sign and ReLU activation functions and, starting from the ReLU function, for max-pooling. The necessary gates include a half-gate generalization for arithmetic GCs, mixed-modulus half gates, mixed-radix addition, and an approximated sign gadget. We then discuss the use of fixed-key AES as a computational-wise optimization in section 4.3.

Afterward, we present our OML approach Sprint step by step along its three abstraction levels, outline our CPU implementation and discuss details of a GPU implementation in chapter 5. Finally, we present the result of the CPU implementation, including discussions about various performance-accuracy tradeoffs, Sprint's online communication overhead, and feature set in chapter 6. In the end, we summarize and present an outlook and ideas for future work in chapter 7.

#### 2.1 Machine Learning

In this section, we introduce the inner workings of ANNs as a generalization of *Linear Regression* (LiR) and *Logistic Regression* (LoR). We end the chapter with a complete description of the inference and training of a small example ANN.

#### 2.1.1 Linear Regression

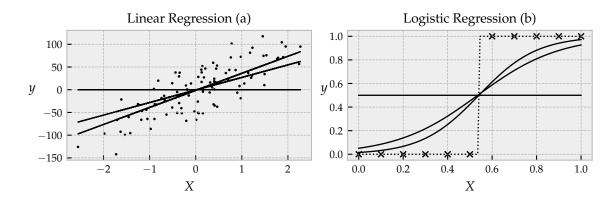

LiR is used in predictive modeling to learn the linear relation between m samples  $X^{m \times n}$ , or more specifically their n features, and a single continuous explanatory variable  $y^m$  of a given dataset (see figure 2.1a).<sup>3</sup> We leverage the *bias-trick* and introduce a weight  $w_0$  and a constant input  $x_{1:n,0} = 1$  to hide the bias inside the weight matrix  $w^{n+1}$ . One option to learn the parameters  $w^{n+1}$  of the model  $f_w(x^{(i)}) = \hat{y}^{(i)} = \sum_{j=1}^n x_j^{(i)} w_j$  is to perform gradient descent<sup>4</sup> on the mean squared error<sup>5</sup>  $J(y, \hat{y}) = \frac{1}{m} \sum_{i=1}^m L(y^{(i)}, \hat{y}^{(i)})$ , with  $L(y^{(i)}, \hat{y}^{(i)}) = \frac{1}{2}(y^{(i)} - \hat{y}^{(i)})^2$ . Gradient descent iteratively updates the model weights with respect to the loss on the training data. Each iteration consists of one update step  $w = w - l \cdot \nabla_w J = w - \frac{l}{m} X^T (Xw - y)$ , with l being the learning rate to control the process's convergence speed. In practice, it is common to use stochastic gradient descent (SGD), where the weights are updated in each iteration with respect to a random subset of the training set, called minibatch. If the batch size is greater than one, the algorithm is called minibatch SGD, which allows leveraging the vectorization capabilities of modern FPUs and speeds up training times.

#### 2.1.2 Logistic Regression

LoR is a *classification algorithm*, which models the probability that a given sample relates to a specific class and outputs a discrete class value (see figure 2.1b).<sup>6</sup> To limit the prediction value between zero and one, meaning the sample is member of the positive or

<sup>&</sup>lt;sup>3</sup>We focus on *simple LiR* with only one explanatory variable.

<sup>&</sup>lt;sup>4</sup>It is also possible to find the optimal parameters for LiR in just one step, leveraging the so-called normal equations.

<sup>&</sup>lt;sup>5</sup>The mean squared error can be derived via maximum likelihood estimation of *w*, assuming the errors per sample being independently gaussian distributed [Mur12].

<sup>&</sup>lt;sup>6</sup>We focus on binary classification ( $y \in \{0, 1\}$ ).

Figure 2.1: Training progress of a LiR and a LoR in the context of example datasets. (a) The LiR was trained over 100 epochs with a learning rate l = 0.01. The model parameters are plotted after initialization, 50 and 100 epochs. (b) The LoR was trained over 200 epochs with l = 0.5, and parameters are plotted after initialization, 100 and 200 epochs. The dotted line shows the final classification border.

negative class, the output of the linear model  $f_w$  is passed through the *logistic activation* function  $\sigma(x) = \frac{1}{1+e^{-x}}$ ;  $g_w(x^{(i)}) = \hat{y}^{(i)} = \sigma(f_w(x^{(i)}))$ . The final classification is then performed using a threshold, typically 0.5. To learn the parameters w, one can again use gradient descent. In case of LoR therefore the *binary cross-entropy*<sup>7</sup>  $J(y, \hat{y}) = \frac{1}{m} \sum_{i=1}^{m} L$ , with  $L(y^{(i)}, \hat{y}^{(i)}) = -(y^{(i)} \log \hat{y}^{(i)} + (1 - y^{(i)}) \log (1 - \hat{y}^{(i)}))$ , is used. This leads to a similar update step of gradient descent, as in LiR:  $w = w - l \cdot \nabla_w J = w - \frac{l}{m} X^T (\sigma(Xw) - y)$ .<sup>8</sup>

#### 2.1.3 Artificial Neuronal Networks

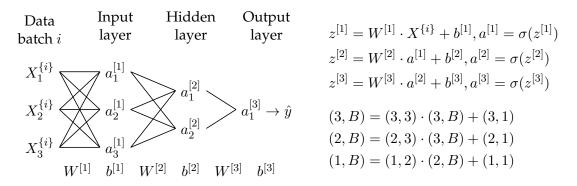

Artificial neural networks (ANN) can be considered as a powerful generalization of LoR. They consist of layers of so-called neurons (see figure 2.2 for a small example), where each of the  $n^{[i]}$  neurons  $a_j^{[i]}$  of layer *i* computes a LoR on the outputs of all neurons of the previous layer i - 1:  $a^{[i]} = \sigma(W^{[i]}a^{[i-1]} + b^{[i]})$ , with  $a^{[0]} = X$  being the input. Note that the bias-trick can also be applied to the training of ANNs, but we omit it here for clarity. Computing this step from the input to the output layer is also referenced as *forward-propagation* and is the only computation needed to perform predictions using a trained ANN. For a mini-batch  $X^{\{i\}}$  of size *B* and the example ANN, forward-propagation is performed via the operations on the right side of figure 2.2. As one can see, the matrix shapes do not

<sup>&</sup>lt;sup>7</sup>The binary cross-entropy can be derived via maximum likelihood estimation of *w*, assuming the samples being independently generated from a Bernoulli distribution [Mur12].

<sup>&</sup>lt;sup>8</sup>It is also possible to find useful parameters for LoR, with many fewer iterations, using Fisher's scoring. If *n* is not too large, this approach converges faster than SGD.

Figure 2.2: Architecture and calculations of example ANN. The left side shows the architecture of the example ANN consisting of three fully connected layers. It expects input samples with three features  $(x_1, x_2, x_3)^T$  and outputs a binary verdict  $\hat{y}$ . The right side shows the calculations for inference as well as the corresponding matrix dimensions.

match when B > 1. To allow B > 1 for training and prediction, in practical ML, a technique called *broadcasting* is used that efficiently "broadcasts" operations such as addition over matrices so that their shapes match [HMvdW<sup>+</sup>20]. In the case of the bias, broadcasting would simulate a matrix of the form (3, B) that repeats the original bias vector *b* times along the second axis and results in a valid matrix addition.

ANNs are usually trained with mini-batch SGD or related optimizers, such as Adam [KB15]. Here we focus on mini-batch SGD with the binary cross entropy as error function. To be able to update the weights  $W^{[i]} = W^{[i]} - l\nabla_{W^{[i]}}J$ , and biases  $b^{[i]} = b^{[i]} - l\nabla_{b^{[i]}}J$ , we have to propagate the error from the output layer via *backward-propagation* to layer *i*, resulting in  $\frac{\partial L}{\partial W^{[i]}} = \frac{\partial L}{z^{[i]}} \cdot a^{[i-1]T}$ , with  $a^{[0]} = X^{\{i\}}$ , and  $\frac{\partial L}{\partial b^{[i]}} = \frac{\partial L}{z^{[i]}}$ . For the example ANN, the weight updates are as follows (for simplicity matrices are shown without the mini-batch indices,  $\odot$  note the element-wise multiplication)

$$\begin{split} \frac{\partial L}{\partial z^{[3]}} &= a^{[3]} - y & (1, B) = (1, B) - (1, B) \\ \frac{\partial J}{\partial W^{[3]}} &= \frac{1}{B} \odot \frac{\partial L}{\partial z^{[3]}} \cdot a^{[2]T} & (1, 2) = (1, 1) \odot (1, B) \cdot (B, 2) \\ \frac{\partial L}{\partial z^{[2]}} &= W^{[3]T} \cdot \frac{\partial L}{\partial z^{[3]}} \cdot \sigma'(a^{[2]}) & (2, B) = (2, 1) \cdot (1, B) \odot (2, B) \\ \frac{\partial J}{\partial W^{[2]}} &= \frac{1}{B} \odot \frac{\partial L}{\partial z^{[2]}} \cdot a^{[1]T} & (2, 3) = (1, 1) \odot (2, B) \cdot (B, 3) \\ \frac{\partial L}{\partial z^{[1]}} &= W^{[2]T} \cdot \frac{\partial L}{\partial z^{[2]}} \cdot \sigma'(a^{[1]}) & (3, B) = (3, 2) \cdot (2, B) \odot (3, B) \\ \frac{\partial J}{\partial W^{[3]}} &= \frac{1}{B} \odot \frac{\partial L}{\partial z^{[1]}} \cdot X^{T} & (3, 3) = (1, 1) \odot (3, B) \cdot (B, 3). \end{split}$$

Before training, the biases are usually initialized to zero, while the weights are set using the *glorot initialization*  $W^{[i]} \sim \sqrt{n^{1-i}}$  (for sigmoid activation) to address the problem of exploding or vanishing gradients [GB10]. In addition to the sigmoid function, a variety of other activations functions exist. Very widely used is the rectified linear unit, short **ReLU** function  $f(x) = \max(0, x)$ , because it can significantly accelerate the training in practice [KO11].

In addition to the fully connected layers described above, a large and dynamic ecosystem of additional layers and model architectures has evolved for a wide range of use cases such as image or natural language processing. While, in the first place, the algorithmic and hardware developments of recent years have made the rapid development in the field of deep learning possible, a selection of powerful frameworks such as TensorFlow [AAB<sup>+</sup>15] (with Keras [C<sup>+</sup>15]), PyTorch [PGM<sup>+</sup>19] and JAX [BFH<sup>+</sup>18] was developed by the open-source community and drive today's deep learning progress. Due to their autodiff modules and performance optimizations, these frameworks enable particularly deep and complex networks to be implemented and trained with minimal effort. For training the models of our experiments, we use TensorFlow and Keras.

#### 2.2 Secure Multiple-Party Computation and Outsourced Machine Learning

In this section, we introduce the field of secure multi-party computation (SMPC) and its relationship to OML. OML is strongly related to the cryptographic area of SMPC<sup>9</sup>, which deals with a setting of two or more parties who jointly compute a given function without revealing their inputs to each other to ensure *privacy* while guaranteeing the *correctness* of the computed results. In contrast to classical cryptography, which often considers attackers from outside, SMPC always considers one or more parties involved in the collective computation of the given function to be *malicious* or at least *curious* about others' private inputs. In this way, the extensively studied and large SMPC research field provides a good theoretical foundation for considering ML outsourcing. Indeed, many SMPC techniques and, in particular, the SMPC attacker models are used to develop OML schemes.

If we neglect the massive computational resource requirements of ML, along with the need for specialized hardware and the increasing importance of side-channel resistance, OML can be viewed as a specialized form of the typical SMPC setting. Specially, because in contrast to SMPC, OML often additionally requires a predefined distribution of the computational workload among the participants. In our case, a client with limited computing capabilities in possession of some data would like to outsource expensive ANN-inference

<sup>&</sup>lt;sup>9</sup>SMPC is also often called SFE: Secure Function Evaluation.

#### 2.2 Secure Multiple-Party Computation and Outsourced Machine Learning

to a server without the server learning anything about the data inputs and possible also demand integrity protection over the computed function to prevent undetected cheating from a malicious server. Obviously, for OML, many different constellations of parties and security objectives are plausible, and we consider further examples in chapter 3. Whereas many different settings for ML outsourcing schemes are thinkable and practically useful, besides the *feasibility* question, the protocols' *efficiency* is crucial. There are many surprising SMPC solutions for different settings that have been presented over the years, but many of these theoretically elegant solutions are by far not efficient enough to

be of practical use. These efficiency difficulties are further amplified by the additional requirements in the OML setting and must be considered in the development and analysis of appropriate schemes.

#### 2.2.1 Ideal/Real Simulation Paradigm

Before we model the capabilities of a potential attacker in the next section, we first define what properties a protocol must satisfy to be considered secure. Hazay et al. [HL10] list the following essential properties, which can be used to cover many if not all multi-party computation tasks and, in this way, also OML:

- *Privacy*: No party should be able to learn more than its outputs from the jointly computed function<sup>10</sup>.

- *Correctness*: The output of each party is correct, meaning the function evaluation can not be tampered from an attacker.

- *Independence of Inputs*: Corrupted parties choose the input independent of the input of honest parties.

- *Guaranteed Output Delivery*: Corrupted parties should not be able to intercept the outputs of honest parties.

- *Fairness*: Corrupted parties get their outputs only when the honest parties get their outputs as well.

While the above list gives a good idea about the rough requirements for an SMPC scheme, it does not provide a security definition. The modern formalization, the *Ideal/Real Simulation Paradigm*, was introduced (not in that terminology) by Goldwasser [GM84] and is

<sup>&</sup>lt;sup>10</sup>That the jointly computed output does not reveal more information than intended is not considered in the SMPC definition and must be ensured separately. In the case of non-trivial functions such as machine learning models, corresponding privacy guarantees can be ensured via the framework of differential privacy [Dwo08, ACG<sup>+</sup>16].

derived via a mental experiment in which an ideal function evaluation via a trusted third party (TTP) is considered. This party performs the computations that should otherwise be computed using the SMPC protocol distributed over all participants. For this purpose, the SMPC protocol participants send their inputs via secure channels to the third party, which in turn performs the necessary computations and sends the appropriate outputs to the corresponding parties.

Obviously, this protocol meets all the security requirements described above, but in the real function-evaluation does not exist a TTP. The simulation paradigm states that a real protocol is secure if no attacker can do more damage in the real function evaluation than in the ideal function evaluation. In other words, a secure protocol should simulate the ideal function evaluation (same input/output distributions). If an attacker can now successfully execute an attack in the real setting, this attacker is also successful in the ideal setting. However, we know that no attacks are possible in the ideal setting and can conclude that the real function evaluation must also be secure. In many settings, as in ours, where half or more of the participants are dishonest, we often can not achieve the output guarantee and fairness requirements and relax the security definition by dropping them.

#### 2.2.2 Attacker Models

To truly comprehend the security achieved by a protocol (or carry out rigorous proofs), it is important to model, in addition to the security requirements, the capabilities of a potential attacker. It must be determined whether benign parties can become dishonest adaptive during protocol execution, known as *adaptive corruption*, or whether they are fixed before the protocol starts, known as *static corruption*. In the OML settings discussed below, we consider only static distributions of dishonest parties and neglect the adaptive case.

It must also be determined whether a dishonest party can deviate from the protocol or not. Therefore one distinguishes between *semi-honest* and *malicious* attackers<sup>11</sup>. The former attacker is weaker and follows the protocol, but receives all internal information from all corrupted parties and tries to learn private information from benign parties. The malicious attacker, on the other hand, can arbitrarily deviate from the protocol to undermine the security requirements of the protocol, and efficiently achieving security in this setting is often much more difficult.

It is natural to question the usefulness of the semi-honest model. One might think, what is the benefit of a security model that requires a potential attacker to be honest and follow the protocol. On the one hand, this model ensures that there are no unintentional

<sup>&</sup>lt;sup>11</sup>Semi-honest attackers are also called honest-but-curious or passive and malicious attackers are also called active or byzantine.

information leaks among honest parties. On the other hand, there are protocols, such as the garbled circuits presented later, for which conversions to the malicious model exist [GMW87, LP07], and the semi-honest model often provides a good stepping stone for such developments.

Last, we also need to model the computational capabilities of the potential attacker. Therefore, we distinguish between the *information-theoretic model* (also known as unconditional or statistical security), in which the attacker has unlimited computational resources and all parties communicate via perfect private channels, and the *computational model*, in which the attacker performs computations in polynomial time and the classical cryptographic assumptions hold. The following discussions refer exclusively to the computational model.

## 2.3 Garbled Circuits

Before we get to the optimizations for GCs, we introduce the Oblivious Transfer and the most basic form of the GC protocol in this chapter.

### 2.3.1 Oblivious Transfer

*Rabin's Oblivious Transfer* (OT) is a protocol between two parties, the sender and the receiver [Rab05]. The sender transfers two bits to the receiver, and the receiver learns only one of them with a probability of 1/2. The other bit becomes oblivious, meaning the receiver can not infer it from the protocol transcript. Besides, the sender cannot recognize which bit the receiver has learned. The *1-out-of-2 Oblivious Transfer* (1-2 OT) [EGL82] behaves the same way, except that the receiver can choose which of the bits he wants to learn. Indeed, Claude Crépeau [Cré87] has shown that both variants are equivalent. Naor and Pinkas [NP99] have shown that the 1-2 OT generalizes efficiently to a 1-*n* OT. In the large and well-studied SMPC field, the Oblivious Transfer has established itself as one of the most important primitives and plays a central role in the protocols presented below.

## 2.3.2 Garbled Circuit Protocol

Garbled circuits (GC) were introduced by Andrew Yao [Yao86] and allow SMPC computations of binary circuits in the two party setting under a semi-honest attacker. Figure 2.3 schematically shows the garbled circuit protocol procedure between a *garbler* Alice and an *evaluator* Bob. Here, the public circuit C should be computed under Alice's private inputs  $x_1$  to  $x_n$  and Bob's private inputs  $y_1$  to  $y_n$ .

In the first step, Alice encrypts the circuit C and her inputs  $x_1$  to  $x_n$  with her secret key<sup>12</sup>

<sup>&</sup>lt;sup>12</sup>The keys used to encrypt wire values of GCs are often also referred to as labels.

| Garbler Alice $A(x_1, \ldots, x_n)$                                                                                                                        | <b>Boolean Circuit</b><br>$C(x_1, \dots, x_n, y_1, \dots, y_n)$            | Evaluator Bob $B(y_1, \ldots, y_n)$                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------|

| $\widetilde{C} = \operatorname{CEn}_{sk}(C)$<br>$\forall i \in [n] : \widetilde{x}_i = \operatorname{IEn}_{sk}^i(x_i)$                                     | $\widetilde{C}, \widetilde{x}_1, \dots, \widetilde{x}_n$                   |                                                                          |

| $\begin{aligned} \forall i \in [n] : \tilde{y}_i^0 &= \mathrm{IEn}_{sk}^i(0) \\ \forall i \in [n] : \tilde{y}_i^1 &= \mathrm{IEn}_{sk}^i(1) \end{aligned}$ | $\forall i \in [n]$ execute                                                |                                                                          |

| $	ilde{y}^0_i, 	ilde{y}^1_i$                                                                                                                               | $\rightarrow \boxed{\begin{array}{c} 1-2-\text{OT} \\ \hline \end{array}}$ | $y_i \in \{0, 1\}$ $\tilde{y}_i^{y_i}$                                   |

| $\underline{\underline{C(x,y)}}$                                                                                                                           | ←                                                                          | $\underline{De(\widetilde{C}, \widetilde{x}_1, \dots, \widetilde{y}_n)}$ |

Figure 2.3: High-level procedure of the garbled circuit protocol.

*sk* and sends them to Bob. Then she encrypts all possible inputs from Bob and transfers the inputs Bob requested to Bob using *n*-times the 1-out-of-2 oblivious transfer. Bob can now evaluate the circuit under the garbled inputs using the evaluation function and sends the result to Alice.

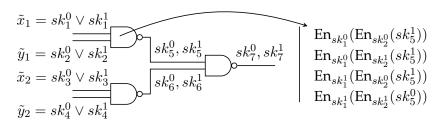

Figure 2.4 shows an example of how the garbling process on circuits works. Every logic gate gets two secret keys  $sk^0$  and  $sk^1$  per input, which correspond to the input of the 0 and 1-bit. Based on the gate's function, the encryption is then performed such that if the evaluator decrypts a gate with its known keys, it receives as output the key that corresponds to the function of the gate. For example, in the case of the first NAND gate at the top left in figure 2.4, the evaluator should only receive the key  $sk_5^0$  if he knows the keys  $sk_1^1$  and  $sk_2^1$ . In addition to the garbled gates, the garbled circuit contains an *output translation table* that assigns the keys at the output of the last gate in the circuit to their bit values. With this table, the evaluator can translate the output keys into their corresponding bit values when evaluating a circuit. The garbling of the inputs runs accordingly and for the circuit from figure 2.4, for example, the following encoding would be a valid garbling: IEn<sub>sk</sub>(1, 1, 0, 0) =  $(sk_1^1, sk_2^1, sk_3^0, sk_4^0)$ .

The evaluator should only learn the correct key per wire to protect the garbler's inputs, and the protocol achieves this via the oblivious transfer. Besides, the evaluator should not be able to distinguish between the keys for the 0 and 1-bit. For this reason, a garbled circuit can only be used with one garbled input combination. Besides, the encryptions per gate must be shuffled. A canonical ordering as in figure 2.4 would expose the key-bit-mapping. To allow the evaluator to still choose the right encryption for its keys from each gate's

Figure 2.4: Example of garbling a small circuit of NAND gates.

Table 2.1: GC optimizations with two-input gates. Size is the number of ciphertexts needed per garbled gate (times k bits, with k being the security parameter). The number of ciphertexts per XOR-gate in fleXOR are dependent on the environment in the circuit. H is a key-derivation function (see also 4.3). Table is taken from [ZRE15].

|                           | Size per Gate |     | Calls to $H$ per Gate |     |           |     |

|---------------------------|---------------|-----|-----------------------|-----|-----------|-----|

| Optimization              |               |     | Generator             |     | Evaluator |     |

|                           | XOR           | AND | XOR                   | AND | XOR       | AND |

| Classical [Yao86]         | 4             | 4   | 4                     | 4   | 4         | 4   |

| Point-and-Permute [BMR90] | 4             | 4   | 4                     | 4   | 1         | 1   |

| Free-XOR [KS08]           | 0             | 4   | 0                     | 4   | 0         | 1   |

| GRR3 [NPS99] + Free-XOR   | 0             | 3   | 0                     | 4   | 0         | 1   |

| GRR2 [PSSW09]             | 2             | 2   | 4                     | 4   | 1         | 1   |

| fleXOR [KMR14]            | {0,1,2}       | 2   | {0,2,4}               | 4   | {0,1,2}   | 1   |

| Half Gates [ZRE15]        | 0             | 2   | 0                     | 4   | 0         | 2   |

| Garbled Gadgets [BMR16]   | 2             | 2   | 3                     | 3   | 1         | 1   |

shuffled ciphertexts, it must be possible for the evaluator to detect the wrong ciphertexts. Such an extension of ciphers is easily possible. For example, one can concatenate the plaintext with a random string before encrypting and publishing it with the ciphers.

GCs are very well studied, improved since their introduction, and besides the simple protocol described here, they have found many different applications, including previously presented OML schemes. For more details and a formal description of GCs see [BHR12].

## 2.4 Garbled Circuit Optimizations

Possible optimizations for GCs focus on the size, the computational complexity, and the hardness assumptions taken to give appropriate security guarantees. As described below and shown in table 2.1, most efforts in recent years have focused on optimizing the size of GCs to reduce the communication complexity between the garbler and the evaluator.

$$\begin{array}{c|c} sk_{1}^{0} \parallel 1, sk_{1}^{1} \parallel 0 & sk_{3}^{0} \parallel 0, sk_{3}^{1} \parallel 1 \\ sk_{2}^{0} \parallel 0, sk_{2}^{1} \parallel 1 & \\ \end{array} \xrightarrow{\hspace{1.5cm}} sk_{2}^{0} \parallel 0, sk_{3}^{1} \parallel 1 & \\ \end{array} \begin{array}{c} \operatorname{En}_{sk_{1}^{1}}(\operatorname{En}_{sk_{2}^{0}}(sk_{3}^{0} \parallel 0)) \\ \operatorname{En}_{sk_{1}^{0}}(\operatorname{En}_{sk_{2}^{0}}(sk_{3}^{0} \parallel 0)) \\ \operatorname{En}_{sk_{1}^{0}}(\operatorname{En}_{sk_{2}^{1}}(sk_{3}^{0} \parallel 0)) \\ \operatorname{En}_{sk_{1}^{0}}(\operatorname{En}_{sk_{2}^{1}}(sk_{3}^{0} \parallel 0)) \end{array}$$

Figure 2.5: Garbling with point-and-permute optimization.

#### 2.4.1 Point-and-Permute

In the classical garbling scheme, in the worst case, the evaluator has to decrypt all four ciphertexts per gate to obtain the correct output label. By introducing the *point-and-permute* optimization in 1990, Beaver et al. [BMR90] reduce the number of necessary decryptions to one ciphertext per gate. To do this, point-and-permute appends a pointer pair  $(p_i, \overline{p_i})$  with  $p_i \in_r \{0, 1\}$  to each key pair  $(sk_i^0 \parallel p_i, sk_i^1 \parallel \overline{p_i})$  and sorts the ciphertexts of the gate in descending order based on the pointer bits<sup>13</sup> (see figure 2.5 for an example). This creates a canonical ordering of the ciphertexts that allows the evaluator to determine the correct gate output with only one decryption without learning any additional information about the input.

#### 2.4.2 Garbled Row-Reduction 3

In 1999, Naor et al. [NPS99] presented the *garbled row reduction 3* (GRR3) optimization, which reduces the number of necessary ciphertexts per gate to three. In the classical GC scheme, the keys  $k_i$  are randomly generated, whereas GRR3 introduces for the first ciphertext per gate (e.g.,  $sk_3^0 \parallel 1$  in figure 2.5) the condition:  $sk_3^0 = (\text{EN}_{sk_1^1}(\text{EN}_{sk_2^0}(0^{k+1})))^{-1}$ . The garbler chooses  $sk_3^0$  such that the corresponding ciphertext equals  $0^{k+1}$ . When the evaluator receives an input with a pointer to the first ciphertext, it can conclude that the plaintext must be the zero-string  $0^{k+1}$ . Therefore, only the last three ciphertexts per gate must be transferred to the evaluator.

#### 2.4.3 Free-XOR

*Free-XOR* was introduced by Kolesnikov and Schneider [KS08] and allows the evaluation of GCs without having to perform cryptographic operations or to transmit ciphertexts for XOR gates<sup>14</sup>. For this the garbler chooses  $sk_i^0$  randomly and  $sk_i^1 = sk_i^0 \oplus R$ , with  $R \in_r \{0,1\}^k$  being a circuit-wide constant. Besides, he sets the output key  $sk_3^0 = sk_1^0 \oplus sk_2^0$ (see figure 2.6 for an overview). Now the output of an XOR gate is the XOR of the two

<sup>&</sup>lt;sup>13</sup>These bits often also called color bits.

<sup>&</sup>lt;sup>14</sup>The use of Free-XOR is restricted by a patent [KS13].

Figure 2.6: Garbling with Free-XOR optimization.

input keys:

$$\begin{split} sk_1^0 \oplus sk_2^0 &= sk_3^0 \\ sk_1^0 \oplus sk_2^1 &= sk_1^0 \oplus (sk_2^0 \oplus R) = (sk_1^0 \oplus sk_2^0) \oplus R = sk_3^0 \oplus R = sk_3^1 \\ sk_1^1 \oplus sk_2^0 &= (sk_1^0 \oplus R) \oplus sk_2^0 = (sk_1^0 \oplus sk_2^0) \oplus R = sk_3^0 \oplus R = sk_3^1 \\ sk_1^1 \oplus sk_2^1 &= (sk_1^0 \oplus R) \oplus (sk_2^0 \oplus R) = (sk_1^0 \oplus sk_2^0) \oplus (R \oplus R) = sk_1^0 \oplus sk_2^0 = sk_3^0 \\ \end{split}$$

Note that Free-XOR introduces a new optimization criterion for GCs. In a circuit consisting of AND, NOT and XOR gates, the number of AND gates should be minimized to obtain an efficient function representation<sup>15</sup>.

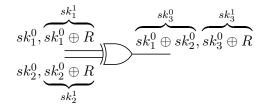

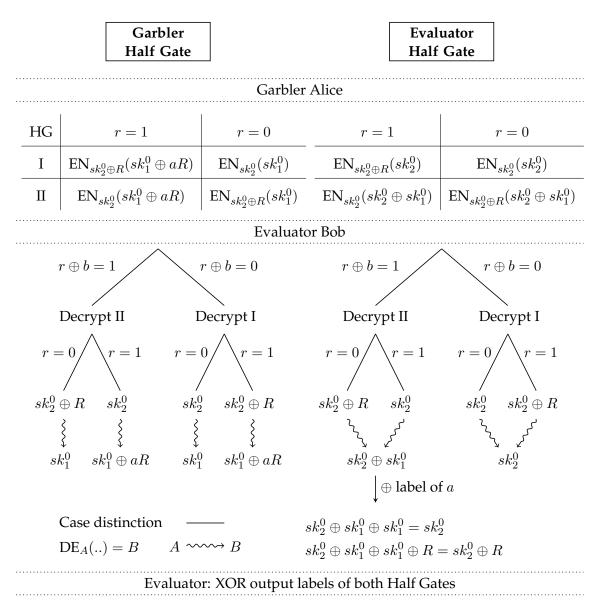

#### 2.4.4 Half Gates

*Garbled row reduction* 2 is an efficient optimization for AND gates needing just two ciphertexts per gate, while Free-XOR allows garbling XOR gates without a single ciphertext. Both optimizations are not compatible with each other. Leveraging Free-XOR and the GRR3 approach, the *Half Gates* (HG) optimization introduced by Zahur et al. in 2015 [ZRE15] accomplish to garble AND gates with only two ciphertexts per gate, while XOR gates remain free<sup>16</sup>. The optimization divides an AND gate into two HGs with two ciphertexts each. Then GRR3 allows to remove one ciphertext per HG.

The application of an HG is shown in figure 2.7. Note that additionally, GRR3 must be applied per HG, such that only two ciphertexts are necessary to garble the whole AND gate. The core idea of the HG optimization is to reformulate the AND operation such that

<sup>&</sup>lt;sup>15</sup>NOT gates are free by incorporating them trough inverted wire-label semantics into their neighboring AND and OR gates.

<sup>&</sup>lt;sup>16</sup>During the thesis, a new optimization was published which beats the HG optimization's lower bound for communication complexity at the price of a higher computational cost [RR21]. In this optimization, only 1.5k + 5 (with *k* being the security parameter) bits are needed for garbling an AND gate. If and to what extent this optimization applies to our use case is an interesting question for future work.

one input is known for each HG:

$$a \wedge b = a \wedge (b \oplus r \oplus r)$$

=

$$\underbrace{(a \wedge r)}_{\text{Garbler Half Gate}} \oplus \underbrace{(a \wedge (b \oplus r))}_{\text{Evaluator Half Gate}}$$

In this reformulation r is a bit randomly chosen by the garbler. For efficiency, one of the point-and-permute bits can be used. In the following, r is the point-and-permute bit of  $sk_2^0$ . Due to the reformulation, the garbler knows one input of the garbler HG (r), and the evaluator knows one input of the evaluator HG  $(b \oplus r)$  - the point-and-permute bit of  $sk_2^b$ . This way, the semantics of the garbler HG simplify to an unary gate. If r is false, the output is false, and if r is true, the output is a. The ciphertexts of the HG are computed accordingly (see table of the garbler HG in figure 2.7).

Garbling the evaluator HG is more involved in the sense that if  $b \oplus r$  is true the evaluator must be able to introduce the truth value a to the HG output. Therefore the garbler sends two ciphertexts  $\text{EN}_{sk_2^0 \oplus R}(sk_2^0)$  and  $\text{EN}_{sk_2^0 \oplus R}(sk_2^0 \oplus sk_1^0)$  if r = 1 or  $\text{EN}_{sk_2^0}(sk_2^0 \oplus sk_1^0)$  and  $\text{EN}_{sk_2^0 \oplus R}(sk_2^0 \oplus sk_1^0)$  if r = 0.

The evaluator selects the ciphertexts to be decrypted from the two HGs based on  $r \oplus b$  (see bottom of figure 2.7). If  $r \oplus b = 1$ , the evaluator XORes the output of the evaluator HG with  $sk_0^a$ . Finally, the AND gate result is obtained by XORing (via Free-XOR) the two HG outputs.

#### 2.5 Trusted Execution Environments

TEEs such as Intel Software Guard Extensions (SGX)[MAB<sup>+</sup>13, CD16, Int21], AMD Secure Encrypted Virtualization (SEV) [Kap16], Sanctum [CLD16], and ARM TrustZone [PS19] allow programs, containers, or whole VMs to be executed securely in hardware-sealed *enclaves*. The hardware isolates the enclave from all other programs on the host, regardless of the privilege level or CPU mode, so it is protected even from a compromised operating system.

The key feature of TEEs besides the enclave isolation is *attestation*, a process that guarantees that a specific enclave, specific in the sense of the code and data it contains, has been deployed on a specific system. One distinguishes between local and remote attestation. With local attestation, two enclaves on the same host authenticate each other. In remote attestation, an enclave authenticates itself to a remote third party. This makes TEEs particularly attractive for use in the typical cloud computing offerings like MLaaS. The cloud provider creates an enclave to which the cloud customer establishes a secure connection and authenticates the enclave via remote attestation.

Figure 2.7: The Half Gate optimization procedure. a and b are the truth values on the input wires of the AND gate. r is the point-and-permute bit of  $sk_2^0$ . To achieve full efficiency, the HGs must be reduced with GRR3, and the XOR of the HG outputs must be performed via Free-XOR.

Like Slalom, we use Intel SGX over AMD SEV to minimize the trusted computing base. SGX applications must be divided by the developer into a trusted and untrusted component. The trusted component runs inside the enclave and communicates with the untrusted part outside the enclave through an interface defined by the developer. The trusted part of the application and the communication between the two components should be kept small to reduce the potential attack surface and improve performance.

After Intel SGX was introduced in Intel Core CPUs in 2015, Intel's current CPU lineup only supports it in 3rd Gen Intel Xeon Scalable server CPUs. While SGX-enabled CPUs in the past only supported 128MB of *Processor Reserved Memory* (PRM), the current Scalable Xeon CPUs can instantiate enclaves up to 1TB in size. This postpones the paging overhead that occurs when the available memory is exceeded. SGX's enclave memory is encrypted, and a memory management engine decrypts data before loading it into registers.

While SGX provides good protection against typical software-based attacks, its design basically does not consider hardware-based side-channel attacks. Over the years, the research community has demonstrated a variety of different side-channel attacks on SGX [BMD<sup>+</sup>17, GESM17, LSG<sup>+</sup>17, WCP<sup>+</sup>17, SCNS16]. However, these hardware-based attacks are usually much more demanding than typical software vulnerabilities. Therefore, SGX, combined with traditional software-based efforts, can significantly raise the bar for successful attacks.

#### 2.6 Graphical Processing Units

Today, *graphical processing units* (GPUs) are mainly sold by Intel, AMD, and Nvidia and were initially designed for rendering real-time 3D graphics. While *central processing units* (CPUs) enable accelerated sequential execution through branch prediction, speculative execution, and large caches, GPUs are designed for massively parallel execution of many similar operations. This concept is also known as *single-instruction-multiple-data* (SIMD). One operation is applied to multiple data elements simultaneously. In the context of Nvidia's *compute unified device architecture* (CUDA) [NBGS08, HP17], it is often also referred to as *single-instruction-multiple-thread* (SIMT). The omission of complex control flow mechanisms and large caches saves chip space and allows thousands of SIMT cores per GPU. Therefore, GPUs offer significantly larger instruction throughput and memory bandwidth compared to CPUs.

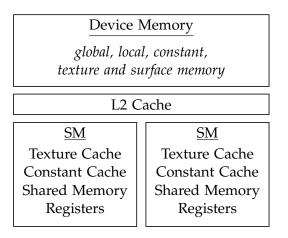

#### 2.6.1 Memory Spaces

From now on, we will look in particular at CUDA-enabled Nvidia GPUs with the so-called CUDA cores. Each GPU has multiple *streaming multiprocessors* (SMs) with multiple CUDA

#### 2.6 Graphical Processing Units

Figure 2.8: Memory hierarchy of CUDA-enabled Nvidia GPUs.

cores. In general, appropriate memory access patterns are the most critical component for the performance of CUDA applications. Therefore, Nvidia's memory hierarchy (see figure 2.8) offers different memory spaces for various access patterns. The *global memory* resides in the *device memory*, which is large but underlies high latency. It is read- and writeable by all threads above all SMs and persistent across kernel launches. A *kernel* is a top-level device function launched by the host and executed by multiple CUDA threads in parallel. In order to achieve the highest possible throughput, the alignment of the data and the *compute capability* (CC) of the GPU must be taken into account in addition to the access pattern when selecting the appropriate memory space (for details, see [Nvi21]). Each GPU has a CC that describes its software and hardware features.

The *local memory* also resides in the device memory and is local to the thread that declares it. Furthermore, the *constant memory* is located in the device memory and is cached SM-wise. Constant memory is read-only within kernels, but the host can write data with the CUDA runtime API. The last memory space in the device memory is the *texture and surface memory*, which is also cached SM-wise. This memory space, or rather its cache, is in particular characterized by spatial 2D-locality.

The *shared memory* is fast on-chip read- and write-memory located in each SM. It is much faster than global and local memory and has much higher bandwidth. To achieve high bandwidth, the shared memory is divided into banks. To prevent bank conflicts, the requests must be scheduled according to the CC of the GPU. For more Nvidia GPU-specific memory features and optimizations, as well as instruction throughput optimizations, see [Nvi21].

Figure 2.9: Execution model of CUDA-enabled Nvidia GPUs.

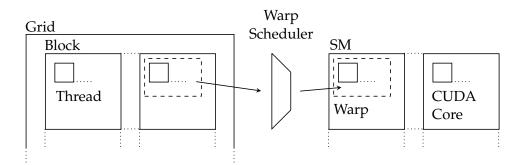

## 2.6.2 General-Purpose Computing

When GPUs are used beyond their original purpose of rendering computer graphics, it is called *general-purpose computing on graphics processing units* (GPGPU). The beginnings of GPGPU were to outsource parallelizable workloads from the CPU to the GPU using graphical primitives. The CUDA toolkit<sup>17</sup> makes it possible to process data without needing a graphical representation via high-performance computing primitives, which are optimized for the Nvidia GPU architecture.

In the typical CUDA workflow, the host generates data. Next, the host copies the data to the device and starts the kernel functions that process the data in parallel with multiple CUDA threads. Usually, one thread processes one data element via one CUDA core. Each thread has a unique identifier for memory-addressing and program flow control. Once the parallelized execution is finished, the results are copied back to the host. Next to explicit functions for host-device data transfers, CUDA also supports the concept of *unified memory*. Unified memory introduces the same view of the memory for the CPU and the GPU and always migrates the data to the processor that needs it.

In CUDA's execution model (see figure 2.9), threads are grouped into so-called *blocks*, and blocks are grouped into so-called *grids*. All blocks in a grid have the same number of threads, and blocks and grids can have up to three dimensions. This partitioning of threads into blocks and grids must be defined by the host when a kernel is started. Threads from the same block share resources such as shared memory and can synchronize and communicate.

CUDA assigns each block to an SM. If there are more blocks than SMs, the remaining blocks must wait. Each block is executed in so-called *warps* of 32 threads. All threads in a warp are executed simultaneously on one SM. The execution context (register values, shared memory, and caches) of a warp remains on the SM for the whole lifetime

<sup>&</sup>lt;sup>17</sup>A popular open-source alternative to CUDA is OpenCL [SGS10].

of the warp. Therefore the warp scheduler can cost-effectively switch between warps to hide memory latency. When the executions of all threads of a block are finished, the SM becomes free, and CUDA schedules a new block until all blocks of the grid have been executed.

Since all threads in a warp share the same program counter, so-called *warp convergence* arises when threads have different program flows, e.g., due to an if condition. In warp convergence, threads with different program flows are executed sequentially and there-fore reduce parallelism and throughput. Besides avoiding warp convergence, the so-called *occupancy* is an essential indicator for utilizing the available CUDA cores. The occupancy is the ratio of active warps to the maximum number of warps that the device supports. Generally, the higher the occupancy, the higher the utilization of the SMs and the higher the throughput. CUDA contains an API for calculating the block size for a maximum occupancy for a given kernel.

Besides the CUDA cores, the current Nvidia GPU generations contain *Tensor cores*, which are particularly useful for accelerating linear algebra workloads. To what extent these special cores can be leveraged for accelerated evaluation of our garbled gates and gadgets is an interesting question for future work [Nvi21].

# **3 Related Work**

Here we summarize important and recent work on OML from a high-level perspective and focus on their key performance aspects regarding the online phase. For each scheme we give an overview, a security analysis, a description of the used methods, and point out the limitations. The input-privacy and model-privacy terms used in the following descriptions refer to privacy in the SMPC setting. Note that without further precautions, an attacker can exploit the prediction services as black box oracles. This enables him to perform model extraction attacks [CJM20, PMG<sup>+</sup>17, TZJ<sup>+</sup>16] to extract model parameters and model inversion [FLJ<sup>+</sup>14, FJR15] or membership inference attacks [SSS517, LBW<sup>+</sup>18, NSH19] to learn training data points or their features. As protection against such attacks, the server could limit possible requests or use the differential privacy framework. These countermeasures are not considered in the OML setting discussed here.

# 3.1 Slalom

Slalom<sup>18</sup> is an OML scheme introduced in 2019 by Tramèr and Boneh [TB19] for verified and private inference on ANNs (with fully connected layers, convolutions, separable convolutions, pooling layers, residual blocks, and activation functions). The scheme is designed for the one-server setting, where the server must feature a CPU with a TEE and an FPU. The one-server setting corresponds to the typical MLaaS case where a remote client wants to outsource expensive ML computations to the cloud. Several schemes for this case which leverage TEEs have been introduced [OSF<sup>+</sup>16, TGS<sup>+</sup>18, HSS<sup>+</sup>18, HZG<sup>+</sup>18, LLP<sup>+</sup>19, ZHC<sup>+</sup>20]. However, Slalom takes a step further and outsources the expensive linear operations of ANN inference from the TEE to an FPU to improve trough-output. To further increase the performance, the protocol is divided into an offline and an online phase. In the offline phase, parts of the integrity check for the computations outsourced to the FPU are pre-computed. If input-privacy with respect to the FPU is required, masking and unmasking bits can also be pre-computed. Slalom's techniques for outsourcing matrix multiplications to an FPU can be easily applied to other ML algorithms.

**Security.** Slalom is secure in the malicious attacker model in terms of the integrity of the computations and optionally the confidentiality of the inputs under the assumption that

<sup>&</sup>lt;sup>18</sup>The name comes from how the TEE and FPU exchange messages for each layer.

## 3 Related Work

the security of the TEE cannot be broken. Also, a commit-and-prove scheme can be used to ensure model-privacy concerning the remote client.

**Methods.** To verify the matrix multiplications outsourced to the FPU, Slalom uses Freivald's algorithm [Fre77]. Thereby Slalom repeatedly reuses the same random vector for the same input samples to minimize the memory usage in the TEE. To achieve optional input-privacy, Slalom uses a simple stream cipher that additively masks all input bits. Compared to the integrity-only approach, the stream encryption generates a significant overhead.

**Limitations.** Since Slalom requires communication between the TEE and FPU after each layer of the ANN, the communication overhead increases with the depth of the ANN. As described by the authors, if Intel SGX is used, the framework is rendered useless at matrix dimensions greater than 4096 due to SGX's DRAM limitation. This limitation drops with the new Intel Xeon Scalable processors, as already described in section 2.5. Compared to purely cryptographic solutions, the use of TEEs widens the surface for possible attacks.

# 3.2 SecureML

SecureML is a 2017 OML scheme by Mohassel and Zhang [MZ17] that allows inference and training (including adaptive learning rate decay and early stopping) on LiR, LoR, and ANNs. The scheme is designed within the two-server model. Here, the data owners distribute their private data to two untrusted but non-colluding servers. These two servers then train the desired model using 2-party SMPC techniques. The protocol is divided into an offline phase, in which multiplication triples are generated, and an online phase for training or inference. Next to SecureML exist a more recent variant called ABY<sup>3</sup> [MR18] which works in the three-server model. Patra et al. [PSSY20] optimize the ABY framework used in SecureML and achieve a significant speedup.

**Security.** SecureML is secure in the semi-honest attacker model under the assumption that the attacker can corrupt any subset of clients, but at most one server. If the clients should be included in the pre-computation of the multiplication triples to accelerate the offline phase, the attacker model changes such that the clients cannot collude with a server. Secure means that the inputs of all data providers remain confidential during and after the computation.

**Methods.** SecureML replaces the SMPC unfriendly activation functions sigmoid and softmax with more efficient and ML-friendly approximations to speed up inference and

## 3.3 Oblivious Neuronal Networks via MiniONN Transformations

learning. While all computations are performed under arithmetic sharing, SecureML uses GCs to speed up the computation of the activation functions. To compute the GCs starting from an arithmetic sharing, SecureML uses a technique from the ABY framework [DSZ15] that allows efficient switching between arithmetic and Yao sharing. For further speedup, SecureML uses vectorization techniques and applies the same multiplication triplets to the same inputs in each epoch.

**Limitations.** All benchmarks in the publication were performed at Amazon Web Services. In a LAN scenario, both servers were positioned in the same region and in a WAN scenario in different regions. The runtimes of these two scenarios differ considerably. To what extent the LAN setting is realistic is certainly questionable. Once the two servers for SecureML are rented from the same cloud provider and no further security measures are implemented, the assumption that these two servers will not collude is extremely strong or even unrealistic. Even though the authors argue that there are scenarios in which geographically separated servers provide a high-speed link, this assumption greatly limits the scheme's practical utility. In addition, the evaluated ANN is very small (2 hidden layers with 128 neurons each) and larger ANNs would result in a huge overhead, making the framework practically unusable.

# 3.3 Oblivious Neuronal Networks via MiniONN Transformations

MiniONN<sup>19</sup> is an approach for secure inference on ANNs in the one-server setting (with convolutions, dropout, dropconnect, batch normalization, ReLU, leaky ReLU, maxout, tanh, sigmoid, max, and mean pooling) and was introduced by Liu et al. in 2017 [LJLA17]. The protocol consists of an offline phase for the pre-computation of dot-product triples (similar to beaver triples; see also section 7.3) and an online phase for prediction.

**Security.** The framework is secure in the semi-honest attacker model under the assumption that either the client or the server is corrupted. It ensures input-privacy w.r.t. the server and model-privacy w.r.t. the client (and calls this property obliviousness).

**Methods.** Utilizing the pre-computed dot-product triples, the server computes the convolution, dropout, dropconnect, and batch normalization layers (all are commonly implemented solely with matrix operations) without additional communication, so that both parties hold valid secret shares after the computation. To compute the activation functions

<sup>&</sup>lt;sup>19</sup>The name means minimizing the overhead for oblivious neuronal network transformations and is inspired by a well-known animation movie.

### 3 Related Work

and max pooling layers, the framework uses GCs and the ABY framework to efficiently switch between arithmetic and Yao sharing. To compute smooth activation functions such as sigmoid, instead of using high-dimensional polynomials that require many SMPC unfriendly multiplications, the framework uses interval-wise approximations with multiple low-degree polynomials. For efficient pre-computation of the dot-product triples, a similar technique as commonly used for pre-computation of Beaver Triples is used.

**Limitations.** Compared to SecureML, the framework is also practical for deeper networks, but compared to Slalom, it does not support FPUs. The evaluation shows that deeper ANNs with seven activation layers or more lead to a large overhead. The authors point out that the prediction accuracy can also increase with increasing model complexity, but saturates above a certain complexity level. They propose an accuracy-overhead tradeoff by considering the number of activation functions used. This tradeoff allows to design deeper models obliviously, but beyond a certain model depth even this approach reaches its limit.

# 3.4 Faster CryptoNets

Faster CryptoNets [CBL<sup>+</sup>18] is a scheme for encrypted inference in the one-server setting. According to the authors Chou et al., it is based on the typical MLaaS setting in which users send inputs to a third-party provider that offers a prediction service on its machine learning models. The scheme supports convolution and fully connected layers, as well as activation functions (ReLU, square, Swish, softplus), scaled average pooling, and batch normalization.

**Security.** The scheme is secure in the malicious attacker model and protects the confidentiality of inputs. The authors refer to this property as oblivious inference.

**Methods.** The methodology of the scheme follows the two previously proposed CryptoNets [GDL<sup>+</sup>16, XBF<sup>+</sup>14] approaches and uses leveled homomorphic encryption (LHE) [RAD<sup>+</sup>78] to perform ANN-inference over encrypted inputs. Following the requirements of ANN-inference, the encryption scheme supports additive and multiplicative homomorphisms. Since the available arithmetic operations prevent typical activation functions, they leverage efficient quantized polynomial approximations. To reduce the number of expensive multiplications, they prune and quantize the ANN.

The practicable multiplicative depth of the LHE scheme limits the ANN to three layers using activation functions. The authors suggest leveraging transfer learning [Ben12, HS06] and computing the inference on the pre-trained layers on the client and the inference on the fine-tuned layers encrypted on the server. They call this approach delegated feature extraction (DFE). To also enable fine-tuning on the client part, they proposed to leverage differential private stochastic gradient descent and improve the accuracy of their scheme noticeably.

**Limitations.** The approximated and quantized activation functions approximate the original activation functions best in the interval [-1,1]. Outside this interval, more significant errors occur. The authors suggest using batch normalization before the activation functions to normalize the inputs to zero mean and unit variance. This works well according to the authors' experiments but limits the model architecture space.

Compared to Slalom, inference times are orders of magnitude slower. The scheme scales relatively poorly, and the DFE approach is interesting but contradicts the MLaaS setting if the goal is to outsource expensive ANN-inference workloads. The authors propose a medical smartphone application as a use case for their system. Whether this is practicable for an inference step with message sizes of several hundred GBs to TBs is questionable.

# 3.5 Delphi

Delphi [MLS<sup>+</sup>20] is an OML scheme for outsourced ANN-inference based on the techniques of Gazelle [JVC18], which leverages LHE for linear and GCs for non-linear ANN layers. It works in the typical MLaaS setting in which a user sends his private input to the prediction API of a cloud provider, which classifies this input using its private ANN model.

**Security.** Delphi is secure in the two-party semi-honest setting, where an adversary corrupts one party. A corrupted client can only learn the output of the inference and the architecture of the ANN. The Planner (see methods) used to replace ReLU activations with approximations leads in an l-layer ANN to a maximal leakage of l-bit training data concerning the client. The authors consider this leakage to be negligible considering the amount of data processed in an ANN. To mitigate this leakage, the authors propose to leverage DP training methods. The server is not able to learn anything about the private inputs of the client.

**Methods.** Delphi is a mixed-SMPC approach with an offline and an online phase. Compared to Gazelle, Delphi reduces the cost of the linear layers by moving the expensive LHE computations via additive SS to the offline phase. Using a planner based on neural

## 3 Related Work

network architecture search [EMH19, WRP19], Delphi replaces suitable ReLU activation functions with approximations while retaining non-approximated ReLUs relevant for accuracy (performance-accuracy tradeoff). Subsequently, hyperparameter optimization is used for the new architecture. Delphi computes ReLU activations via GCs (OT in the offline phase) and ReLU approximations with quadratic polynomials via Beaver Triples (see section 7.3) (precomputed with linear HE in the offline phase). Delphi utilizes standard GPU libraries for the acceleration of linear layers.

**Limitations.** The use of non-standard activation functions complicates training and limits the space of possible model architectures. The neural network architecture search leads to a significant training overhead. ANNs cannot always be re-trained, for example, the training data may no longer be available, or the training cost may be too high.

# 4 Garbling Techniques for Sprint

In this chapter, we introduce the garbling techniques for Sprint based on the binary GCs an their optimizations introduced in section 2.3 and section 2.4.

## 4.1 Garbling Gadgets for Arithmetic Circuits

Implementing arithmetic operations via conventional binary GCs is expensive, especially compared to other SMPC approaches like secret-sharing-based SMPC. Ball, Malkin, and Rosulek [BMR16] introduced garbling gadgets for efficient garbling of arithmetic circuits over large finite fields. Considering our use case, their gadgets allow, in particular, free addition (mod m), free multiplication with a constant (mod m), and efficient projection gates for arbitrary unary functions (mod m). Starting from Free-XOR, Ball et al. consider wire-labels as vectors of components from  $\mathbb{Z}_m$ . The encoding of a value  $x \in \mathbb{Z}_m$  is given through  $sk^x = sk^0 + xR_m$ , with  $R_m$  being a circuit-wide constant vector of random elements from  $\mathbb{Z}_m^{20}$ . The construction considers wires with different moduli, called *mixed moduli circuits*, and leverages different offsets  $R_m$  for each module m - but wires of one modulus always share the same offset value. Point-and-permute generalizes by using an element from  $\mathbb{Z}_m$  instead of a single bit and choosing  $1 \in \mathbb{Z}_m$  as the point-and-permute component of  $R_m$ .

A mixed modulus circuit consists of an acyclic structure of wires together with their moduli and gates constructed as follows (we limit the description to gates relevant for our use case):

- Addition  $(x + y) \mod m$  (unbounded fan-in with equal modulus):  $sk_1^x + sk_2^y \equiv (sk_1^0 + sk_2^0) + (x + y)R_m \mod m.$

- Multiplication by a public constant *xc* mod *m* (unary gate):

*c* · *sk<sup>x</sup>* ≡ *c* · *sk*<sup>0</sup> + *cxR<sub>m</sub>* mod *m* with *c* being coprime to modulus *m* (needed for technical reasons in the security proof, see also [BMR16]).

- Unary projection gate for arbitrary functions φ : Z<sub>m</sub> → Z<sub>n</sub>: A garbled projection gate consists of *m* ciphertexts of the form En<sub>sk<sup>x</sup></sub>(sk<sup>φ(x)</sup>). Leveraging GRR3, one ciphertext can be removed.

<sup>&</sup>lt;sup>20</sup>This Free-XOR generalization together with the free addition gate was shown before, e.g. in [MPS15].

#### 4 Garbling Techniques for Sprint

While the first two gate types are free, the projection gate is not practical for larger moduli m. BMR, therefore, propose to use a *composite primal modulus* (CPM)  $P_k = 2 \cdot 3 \cdot \ldots \cdot p_k$ , the product of the first k primes and to leverage the Chinese remainder theorem to represent the wire values in a *residue representation*<sup>21</sup>:

$$\llbracket x \rrbracket_{crt} = ([x]_2, [x]_3, \dots, [x]_{p_k}), \text{ where } [x]_m \text{ represents } x \mod m.$$

From the circuit perspective, every value of a conventional wire is now represented by a bundle of wires, with each of the wires in a bundle applying one factor of the CPM. BMR show how to transfer various operations efficiently into the domain of the residue representation. We will return to the residue representation in the next section and show operations that capitalize on it. At this point, we are only interested in how the addition and multiplication operations described above remain free:

• Addition mod *m*:

$$\llbracket x \rrbracket_{crt} + \llbracket y \rrbracket_{crt} = ([x]_2, [x]_3, \dots, [x]_{pk}) + ([y]_2, [y]_3, \dots, [y]_{pk})$$

$$= ([x]_2 + [y]_2, [x]_3 + [y]_3, \dots, [x]_{pk} + [y]_{pk})$$

$$= \llbracket x + y \rrbracket_{crt}$$